# The principles of Spread Spectrum communication

More information on spread spectrum can be found in my thesis: <u>Non-Cellular Wireless Communication</u> Systems.

In Code Division Multiple Access (CDMA) systems all users transmit in the same bandwidth simultaneously. Communication systems following this concept are `spread spectrum systems'. In this transmission technique, the frequency spectrum of a data-signal is spread using a code uncorrelated with that signal. As a result the bandwidth occupancy is much higher then required.

The codes used for spreading have low cross-correlation values and are unique to every user. This is the reason that a receiver which has knowledge about the code of the intended transmitter, is capable of selecting the desired signal.

A number of advantages are:

- Low power spectral density. As the signal is spread over a large frequency-band, the Power Spectral Density is getting very small, so other communications systems do not suffer from this kind of communications. However the Gaussian Noise level is increasing.

- Interference limited operation. In all situations the whole frequency-spectrum is used.

- **Privacy due to unknown random codes.** The applied codes are in principle unknown to a hostile user. This means that it is hardly possible to detect the message of an other user.

- Applying spread spectrum implies the reduction of multi-path effects.

- Random access possibilities. Users can start their transmission at any arbitrary time.

- Good anti-jam performance.

Because of the difficulty to jam or detect spread spectrum signals, the first applications were in the military field. However nowadays spread spectrum systems are gaining popularity also in commercial applications.

The main parameter in spread spectrum systems is the processing gain: the ratio of transmission and information bandwidth:

$$G_P = \frac{BW_t}{BW_s} \tag{1}$$

which is basically the "spreading factor". The processing gain determines the number of users that can

be allowed in a system, the amount of multi-path effect reduction, the difficulty to jam or detect a signal etc. For spread spectrum systems it is advantageous to have a processing gain as high as possible.

There exist different techniques to spread a signal: Direct-Sequence (DS), Frequency-Hopping (FH), Time-Hopping (TH) and Multi-Carrier CDMA (MC-CDMA) [YLF94]. It is also possible to make use of combinations of them. An overview of the more conventional spread spectrum techniques can be found in [SOSL85a,Hol82,Dix84,PSM82,SH85].

We will now concentrate on the two most popular techniques: Direct-Sequence and Frequency-Hopping.

### **Direct Sequence**

Direct Sequence is the best known Spread Spectrum Technique. The data signal is multiplied by a Pseudo Random Noise Code (PNcode).

A PNcode is a sequence of chips valued -1 and 1 (polar) or 0 and 1 (non-polar) and has noise-like properties. This results in low cross-correlation values among the codes and the difficulty to jam or detect a data message [Gol67,HdV71,Roe77,Gla92].

Several families of binary PNcodes exist, they are addressed in another <u>section</u>. A usual way to create a PNcode is by means of at least one shift-register. When the length of such a shift-register is n, the following can be said about the period  $N_{DS}$  of the above mentioned code-families:

$$N_{\rm DS} = 2^n - 1. (2)$$

In direct-sequence systems the length of the code is the same as the spreading-factor with the consequence that:

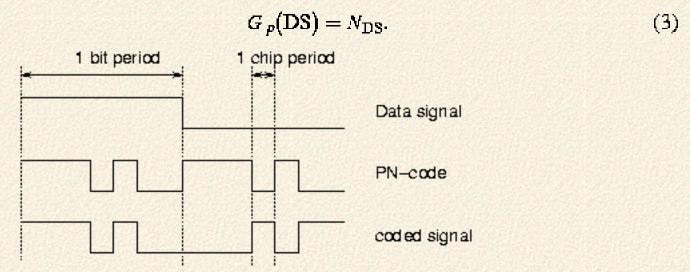

Figure 1: direct-sequence spreading

This can also be seen from figure  $\underline{1}$ , where we show how the PNcode is combined with the data-signal, in this example  $N_{DS} = 7$ . The bandwidth of the data signal is now multiplied by a factor  $N_{DS}$ . The power contents however stays the same, with the result that the power spectral density lowers.

The generation of PNcodes is relatively easy, a number of shift-registers is all that is required. For this reason it is easy to introduce a large processing-gain in Direct-Sequence systems.

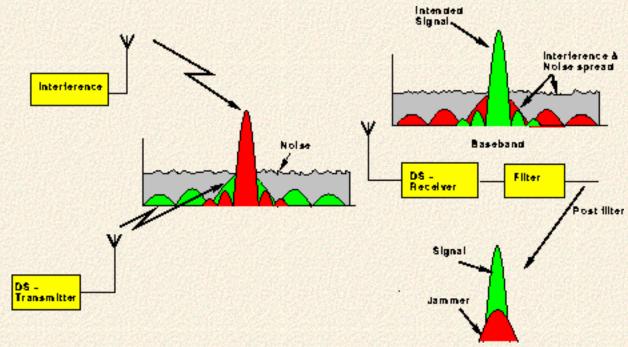

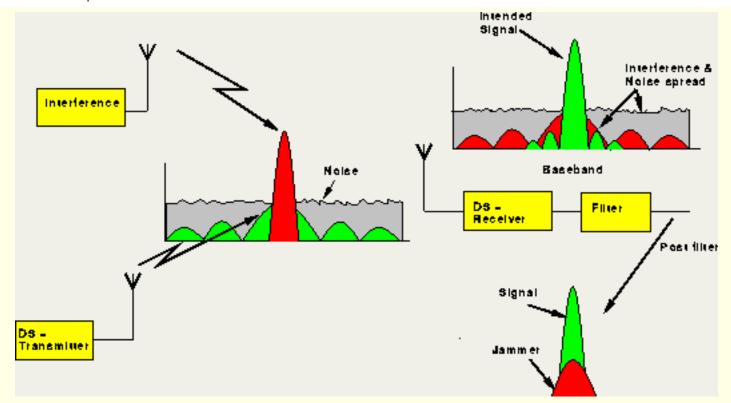

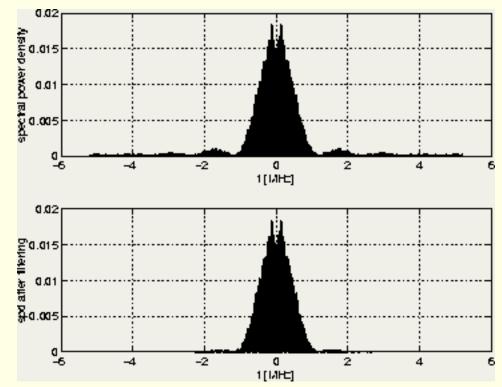

Figure 2: DS-concept, before and after despreading

In the receiver, the received signal is multiplied again by the same (synchronized) PNcode. Since the code existed of +1s and -1s, this operation completely removes the code from the signal and the original data-signal is left. Another observation is that the despread operation is the same as the spread operation. The consequence is that a possible jamming-signal in the radio channel will be spread before data-detection is performed. So jamming effects are reduced (see figure 2 [Hen84]).

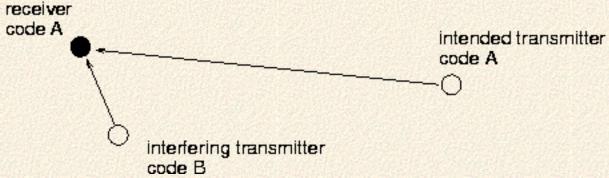

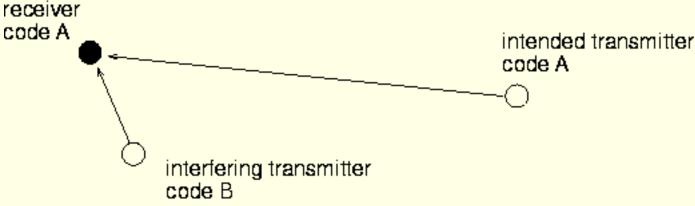

The main problem with applying Direct Sequence spreading is the so-called Near-Far effect which is illustrated in figure 3. This effect is present when an interfering transmitter is much closer to the receiver than the intended transmitter. Although the cross-correlation between codes A and B is low, the correlation between the received signal from the interfering transmitter and code A can be higher than the correlation between the received signal from the intended transmitter and code A. The result is that proper data detection is not possible.

Figure 3: near-far effect illustrated

Another spread spectrum technique: Frequency-Hopping is less effected by this Near-Far effect.

### **Frequency Hopping**

When applying Frequency Hopping, the carrier frequency is 'hopping' according to a unique sequence (an FH-sequence of length  $N_{\rm FH}$ ). In this way the bandwidth is increased by a factor  $N_{\rm FH}$  (if the channels are non-overlapping):

$$G_p(\mathrm{FH}) = N_{\mathrm{FH}}.$$

(4)

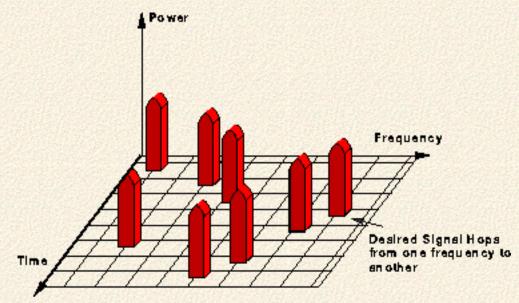

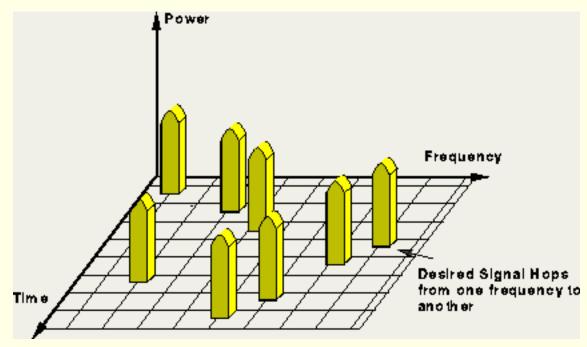

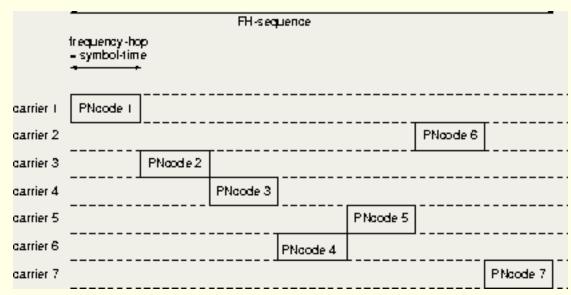

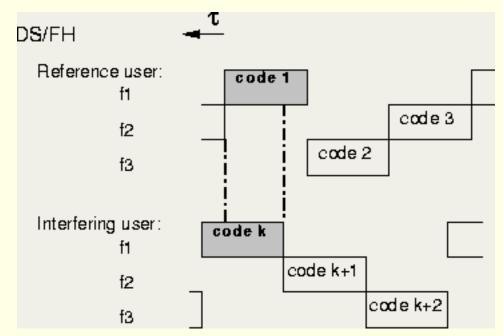

The process of frequency hopping is illustrated in figure 4. A disadvantage of Frequency-Hopping as opposed to Direct-Sequence is that obtaining a high processing-gain is hard. There is need for a frequency-synthesizer able perform fast-hopping over the carrier-frequencies. The faster the `hopping-rate" is, the higher the processing gain.

Figure 4: illustration of the frequency hopping concept

On the other hand, Frequency-Hopping is less effected by the Near-Far effect than Direct-Sequence. Frequency-Hopping sequences have only a limited number of `hits" with each other. This means that if a near-interferer is present, only a number of `frequency-hops" will be blocked in stead of the whole signal. From the `hops" that are not blocked it should be possible to recover the original data-message.

### **Hybrid System: DS/(F)FH**

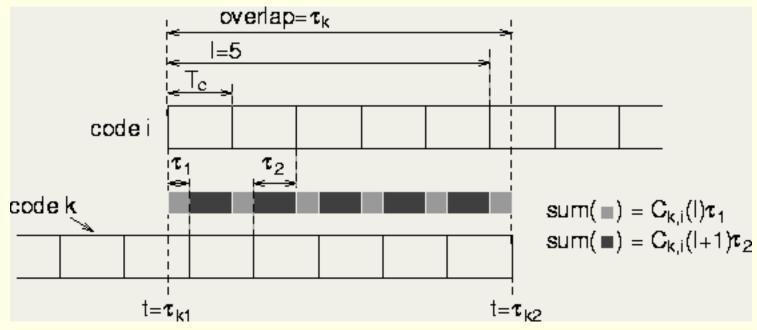

The DS/FFH Spread Spectrum technique is a combination of direct-sequence and frequency-hopping. One data bit is divided over frequency-hop channels (carrier frequencies). In each frequency-hop channel one complete PN-code of length is multiplied with the data signal (see figure, where is taken to be 5).

Figure 5: ds-fh spreading scheme

carrier ?

As the FH-sequence and the PN-codes are coupled, an address is a combination of an FH-sequence and PN-codes. To bound the hit-chance (the chance that two users share the same frequency channel in the same time) the frequency-hop sequences are chosen in such a way that two transmitters with different FH-sequences share at most two frequencies at the same time (time-shift is random).

PNoode 7

### **Pseudo-Random Noise Codes**

A PNcode used for DS-spreading exists of  $N_{\rm DS}$  units called chips, these chips can have 2 values: -1/1 (polar) or 0/1. As we combine every data symbol with a complete PNcode, the DS processing gain is equal to the code-length. To be usable for direct-sequence spreading, a PNcode must meet the following constraints:

- The sequences must be build from 2-leveled numbers.

- The codes must have a sharp (1-chip wide) autocorrelation peak to enable code-synchronization.

- The codes must have a low cross-correlation value, the lower this cross-correlation, the more users we can allow in the system. This holds for both full-code correlation and partial-code correlation. The latter because in most situations there will not be a full-period correlation of two codes, it is more likely that codes will only correlate partially (due to random-access nature).

- The codes should be `balanced": the difference between ones and zeros in the code may only be 1. This last requirement stands for good spectral density properties (equally spreading the energy over the whole frequency-band).

Codes that can be found in practical DS-systems are: Walsh-Hadamard codes, M-sequences, Gold-codes and Kasami-codes. These code sets can be roughly divided into two classes: orthogonal codes and non-orthogonal codes. Walsh sequences [Bea75] fall in the first category, while the other group contains the so-called shift-register sequences [Gol67,Roe77,SP80].

#### **Walsh Hadamard codes**

Walsh-sequences have the advantage to be orthogonal, in this way we should get rid of any multi-access interference. There are however a number of drawbacks:

- The codes do not have a single, narrow autocorrelation peak.

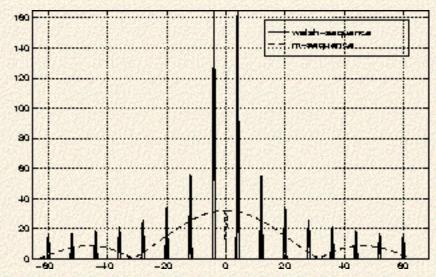

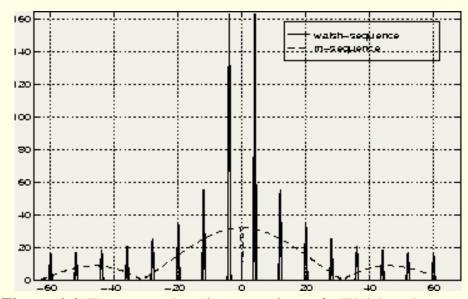

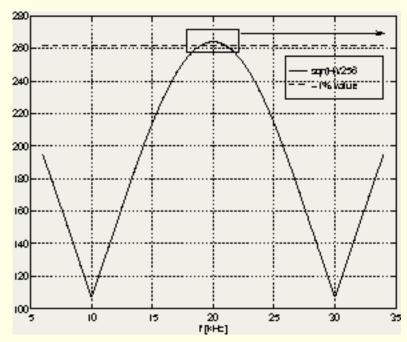

- The spreading is not over the whole bandwidth, instead the energy is spread over a number of discrete frequency-components. This can be seen from the solid line in figure 6.

- Although the full-sequence cross-correlation is identically zero, this does not hold for partial-sequence cross-correlation function. The consequence is that the advantage of using orthogonal codes is lost.

- Orthogonality is also affected by channel properties like multi-path. In practical systems equalization is applied to recover the original signal.

Figure 6: frequency-domain comparison of a Walsh and an M-sequence

These drawbacks make Walsh-sequences not suitable for non-cellular systems. Systems in which Walsh-sequences are applied are for instance multi-carrier CDMA [YLF94] and the cellular CDMA system IS-95 [Qua92]. Both systems are based on a cellular concept, all users (and so all interferers) are synchronized with each other. Multi-Carrier CDMA uses another way of spreading while IS-95 uses a combination of a Walsh-sequence and a Shift-Register sequence to enable synchronization.

#### **Shift-Register sequences**

Shift-Register sequences are not orthogonal, but they do have a narrow autocorrelation peak. The name already makes clear that the codes can be created using a shift-register with feedback-taps. By using a single shift-register, maximum length sequences (M-sequences) can be obtained. Such sequences can be created by applying a single shift-register with a number of specially selected feedback-taps. If the shift-register size is n then the length of the code is equal to  $2^n - 1$ . The number of possible codes is dependent on the number of possible sets of feedback-taps that produce an M-sequence. These sequences have a number of special properties, here we will mention some of them which will be used in the code selection process.

• M-sequences are balanced: the number of ones exceeds the number of zeros with only 1.

- The spectrum of an M-sequence has a **sync**<sup>2</sup>-envelope. In figure 6 the spectra of a Walsh-sequence of length 64 and an M-sequence of length 63 are shown, both sequences contain (almost) the same power. The figure shows that applying an M-sequence better distributes the power over the whole available frequency range.

- The shift-and-add property can be formulated as follows:

$$T^k u = T^i u \ T^j u \tag{5}$$

here u is an M-sequence, by combining two shifts of this sequence (relative shifts i and j) we obtain again the same M-sequence, yet with another relative shift.

• The auto-correlation function is two-valued:

$$R_u(\tau) = \begin{cases} N & \tau = kN \\ -1 & \tau \neq kN \end{cases} \tag{6}$$

where k is an integer value, and T is the relative shift.

- There is no general formula for the cross-correlation of two M-sequences, only some rules can be formulated [Roe77].

- A so called "preferred pair" is a combination of M-sequences for which the cross-correlation only shows 3 different values: -1,  $-2\lfloor (n+2)/2 \rfloor$  and  $2\lfloor (n+2)/2 \rfloor$ . There do not exist preferred pairs for shift-registers with a length equal to 4k where k is an integer.

Combining two M-sequences which form a "preferred pair" leads to a so-called Gold-code. By giving one of the codes a delay with respect to the other code, we can get different sequences. The number of sequences that are available is  $2^n + 1$  (the two M-sequences alone, and a combination with  $2^n - 1$

different shift positions). The maximum full-code cross-correlation has a value of  $2^{\lfloor (n+2)/2 \rfloor} + 1$ .

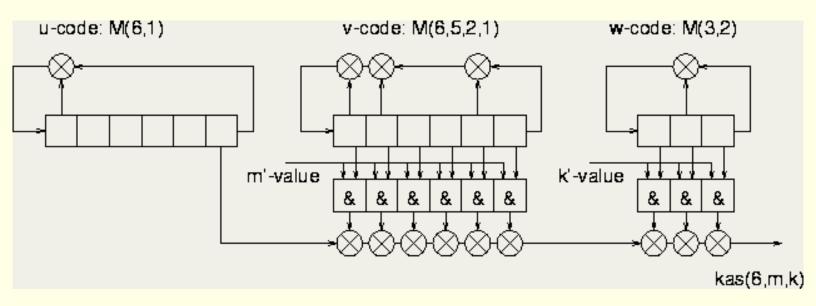

If we combine a Gold-code with a decimated version of one of the 2 M-sequences that form the Gold-code we obtain a ``Kasami-code' from the large set. Such a code can then be formulated as follows:

$$c = \mathbf{u} \cdot T^k \mathbf{v} \cdot T^m \mathbf{w} \tag{7}$$

here u and v are M-sequences of length:  $N_{DS} = 2^n - 1$  (n even) which form a preferred pair. w is a

M-sequence resulting after decimation the v-code with a value  $2^{n/2} + 1$ . T denotes a delay of one chip, k

is the offset of the v-code with respect to the u-code and m is the offset of the w-code with respect to the u-code. Offsets are relative to the all-ones state.

In the large set of Kasami-codes a number of ``special cases" can be observed. The two M-sequences that are used as a basis are part of the set, as well as the Gold-codes that can be created using these M-sequences. Also a sub-set of the large set of Kasami-codes is the so-called small set of Kasami-codes: this set can be obtained by combining an M-sequence with the decimated version of itself, so leaving out

Spread Spectrum Techniques

the other M-sequence.

Kasami-codes have the same correlation properties as Gold-codes, the difference lays in the number of codes that can be created. For the large set of Kasami-codes this number is equal to  $2^{n/2}(2^n + 1)$ .

Choosing n equal to for instance 6 leaves us 520 possible codes. It is important to have a large code-set: the number of available codes determines the number of different code addresses that can be created. Also a large code-set enables us to select those codes which show good cross-correlation characteristics.

Last modified on August 29, 1996 by <u>Jack Glas</u>

## Non-Cellular Wireless **Communication Systems**

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof. ir. K.F. Wakker, in het openbaar te verdedigen ten overstaan van een commissie, door het College van Dekanen aangewezen, op donderdag 5 december 1996 te 10.30 uur

door

#### **Jacobus Petrus Franciscus GLAS**

elektrotechnisch ingenieur geboren te Haarlemmermeer

- Contents

- List of Figures

CAS HOME

- Summary

- Preface

- Introduction

- o Multi-Access

- o CDMA techniques

- Claims of the thesis

- o Overview

- An Embedded Spread Spectrum Processor

- Introduction

- Why an Embedded Realization?

- The design process

- Selecting a Processor-Framework

- o Requirements for the Hardware/Software partitioning stage

- Available resources

- Conclusions

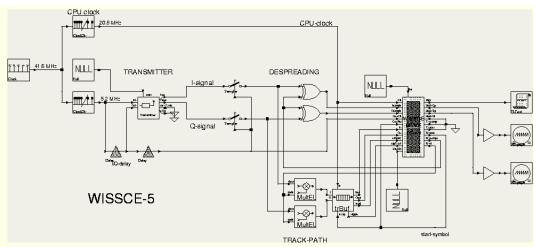

- Hybrid DS/FH Spread Spectrum Communication System

- o Introduction

- System Specification

- Clock control

- Fixing the system parameters for wissce

- Conclusion

- Performance analysis

- Introduction

- O Degradation of the data detection snr

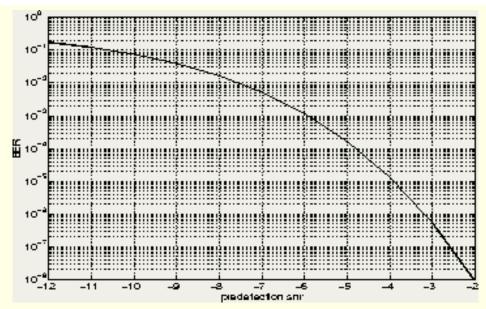

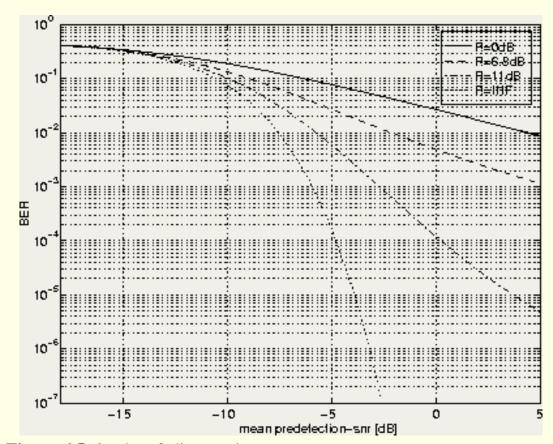

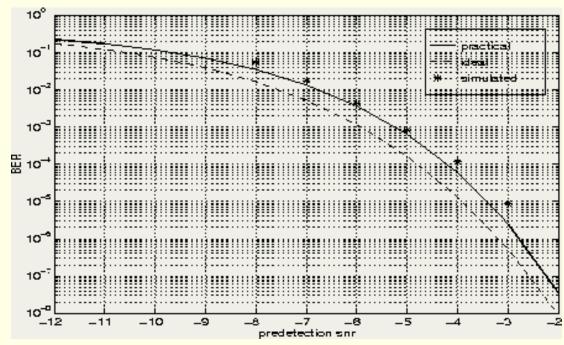

- O Relation between *snr*-in and the *ber*-performance

- Code selection

- o Conclusion

- Implementation alternatives

- o Introduction

- o Data detection

- Synchronization

- Front-end considerations

- Conclusions

- Hardware/Software partitioning

- o Introduction

- o System description

- o Partitioning process

- Conclusions

- WISSCE on the MOVE

- Introduction

- o Hardware design

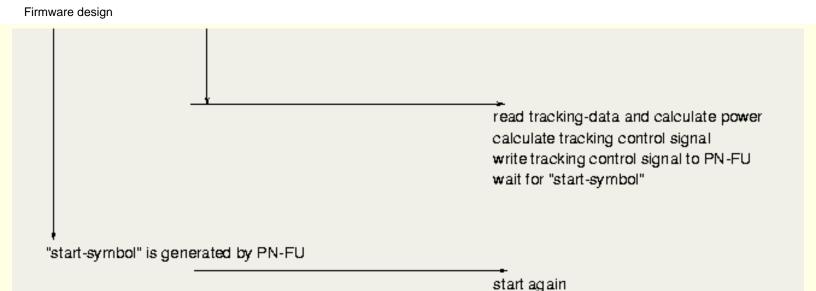

- o <u>Firmware design</u>

- o Co-Simulation

- Conclusions

- Conclusions

- Pseudo-Random Noise Sequences

- o Selected Code-set

- o Implementing the relative delays

- References

- Index

- Samenvatting

- About the author

Copyright © 1996 by <u>Jack P.F. Glas</u>. All rights reserved. No part of this book may be reproduced in any form or by any electronic or mechanical means (including photocopying, recording, or information storage and retrieval) without prior permission in writing from the author. An exception is made for retrieval from the World Wide Web for personal use only.

The ISBN-number of the "paper"-version of this thesis is: 90-5326-024-2

This page has been visited times and was last modified on Tue February 18, 1997. Comments and questions can be addressed to the <u>WWW Coordinator</u>.

Contact the <u>Webmaster</u> if you have any technical problems.

Next: <u>List of Figures</u> Up: <u>Non-Cellular Wireless Communication Systems</u> Previous: <u>Non-Cellular</u> Wireless Communication Systems

### **Contents**

- List of Figures

- Summary

- Preface

- Introduction

- o Multi-Access

- o CDMA techniques

- Direct Sequence

- **■** Frequency Hopping

- Claims of the thesis

- Concept development of communication systems

- Implementation issues in a -receiver

- Building a transceiver as an embedded system

- o Overview

- An Embedded Spread Spectrum Processor

- o Introduction

- Why an Embedded Realization?

- o The design process

- o Selecting a Processor-Framework

- bus width

- number of busses

- width of address-bus

- number of register-units

- o Requirements for the Hardware/Software partitioning stage

- o Available resources

- Conclusions

- Hybrid DS/FH Spread Spectrum Communication System

- Introduction

- System Specification

- Frequency bands

- Transmission capacity

- CDMA technique

- Modulation format

- Front-end related issues

- Bit Error Probability

- Analog to digital interfacing

- Clock control

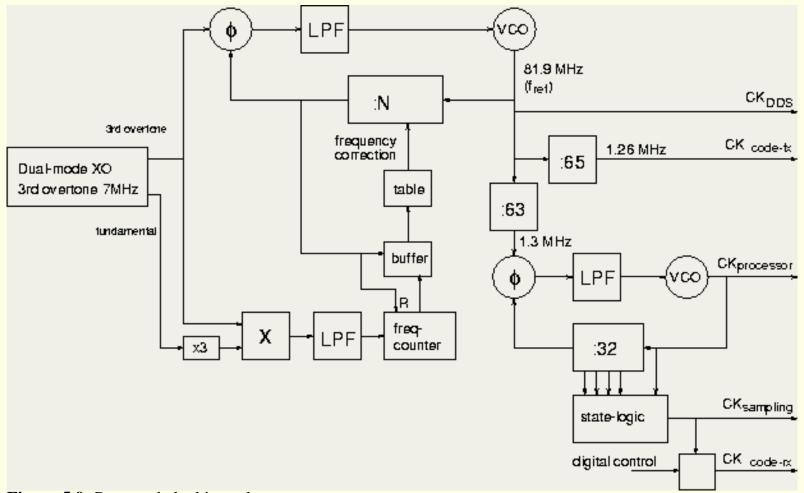

- Front-end clocks

- *fh*-synthesizer clock

- Baseband processing clocks

- Sample-clock signals

- Processor clock signals

- Code-clocks

- Fixing the system parameters for wissce

- System related issues

- Clock related issues

- Conclusion

- Performance analysis

- Introduction

- O Degradation of the data detection *snr*

- <u>Influences of non-ideal despreading</u>

- <u>Influences of Multi-Access Interference</u>

- Far interference

- Near interference

- Conclusion

- O Relation between *snr*-in and the *ber*-performance

- Performance analysis in an additive Gaussian noise channel.

- Performance analysis in a multi-path channel

- Fading Channels

- Influences of the fading channel

- Conclusions

- o Code selection

- Choosing a *pn-code*

- Choosing a code-family

- Walsh Hadamard codes

- Shift-Register sequences

- Choosing a code-set with good cross-correlation properties

- <u>Implementation issues</u>

- Conclusions

- Choosing an *fh-sequence*

- The hit-probability

- Conclusion

- Implementation alternatives

- o Introduction

- Data detection

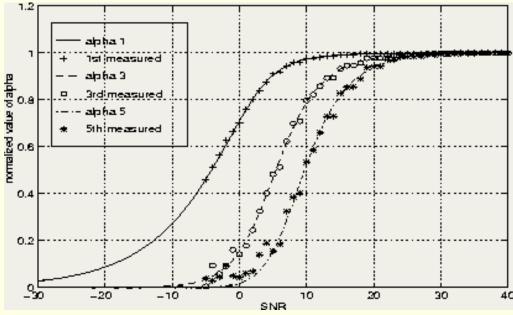

- Complexity reduction of the data detection algorithm

- 3-leveled Twiddle-Factors

- Limiting of the input signal

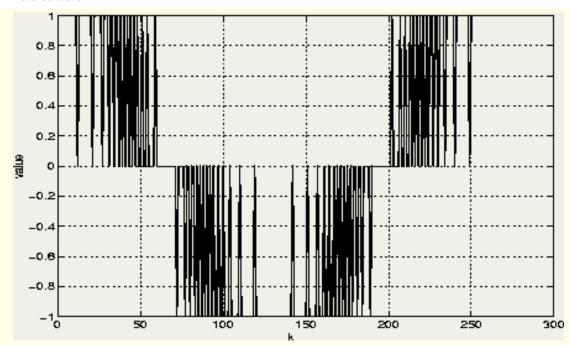

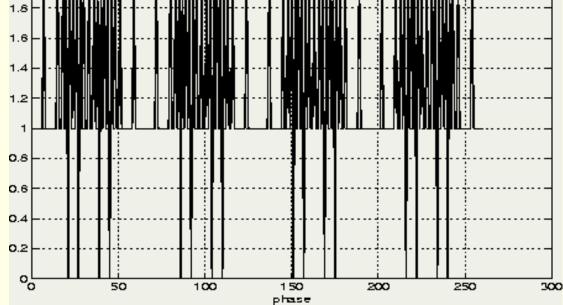

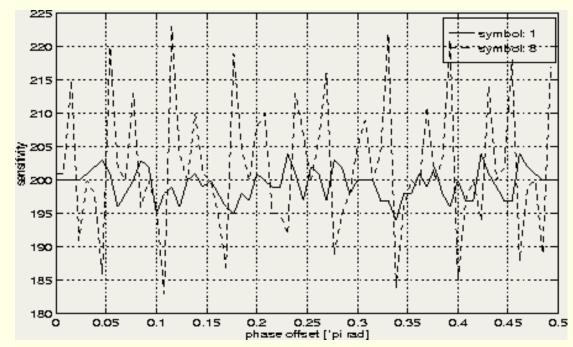

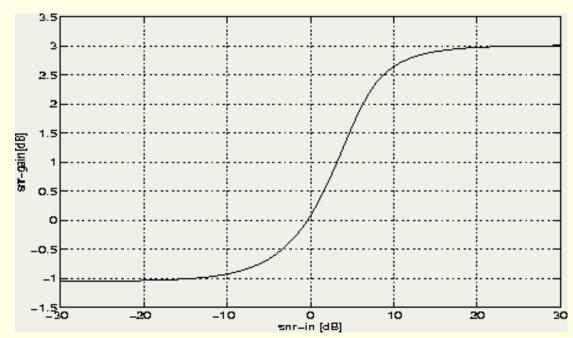

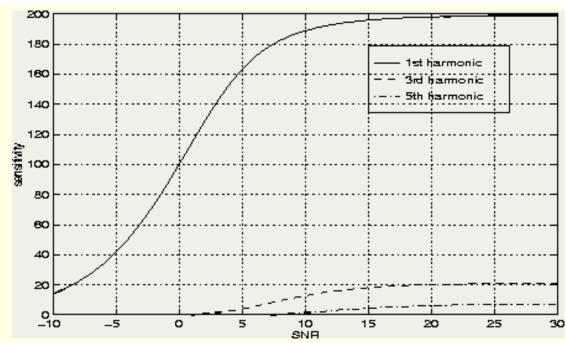

- Sensitivity

- Phase-dependence

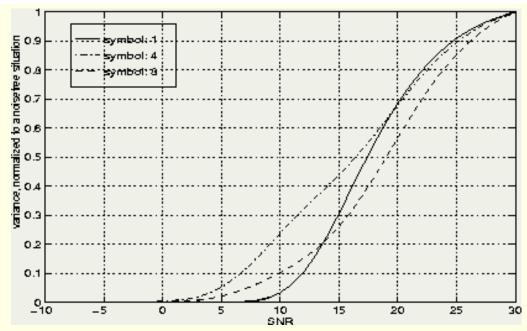

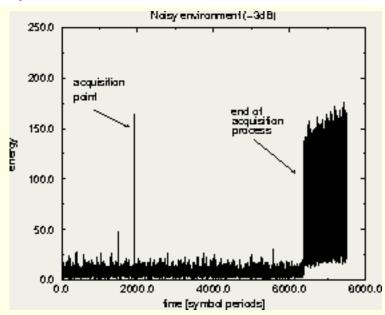

- Noisy environments

- Performance analysis

- Conclusion

- Synchronization

- Carrier-synchronization

- Code-synchronization

- Acquisition

- Acquisition strategy

- Acquisition algorithm

- Implementation issues

- Conclusion

- Code-tracking

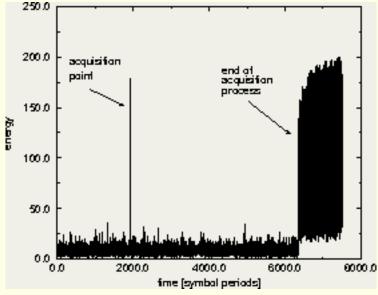

- Code-tracking algorithm

- Implementation issues

- Conclusion

- Front-end considerations

- Introduction

- Amplification

- Channel selection and frequency translation

- **■** Filtering

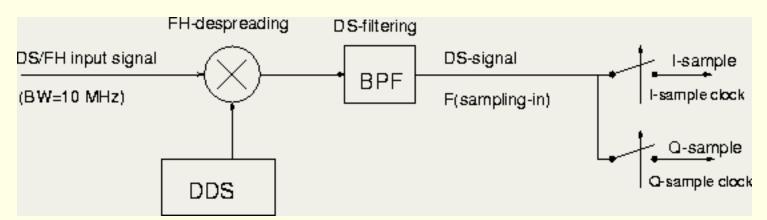

- Removal of the spread spectrum coding

- Considerations

- Conclusions

- Conclusions

- Hardware/Software partitioning

- o Introduction

- o System description

- Deriving the *sir*-graph and profiling information

- Deriving cost-functions

- Constraints

- o Partitioning process

- o Conclusions

- WISSCE on the MOVE

- Introduction

- Hardware design

- Processor framework

- Application specific hardware

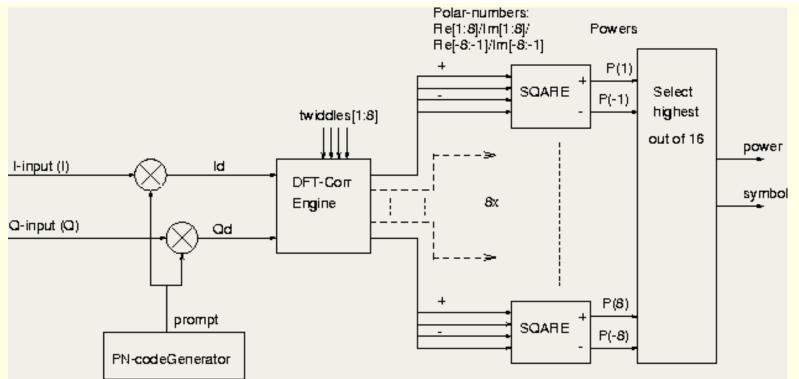

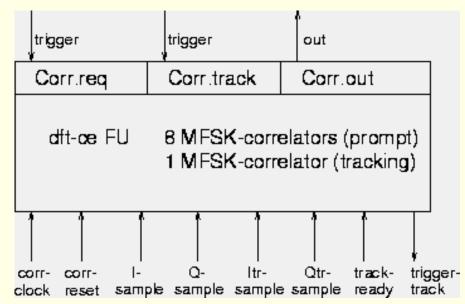

- <u>mfsk</u>data-detection fu

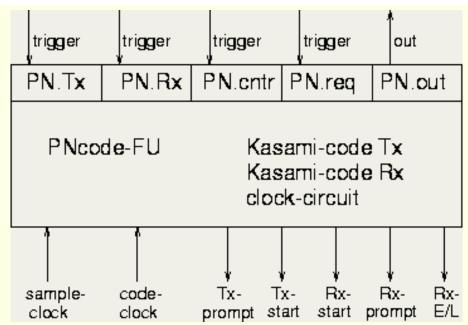

- Code generation *fu*

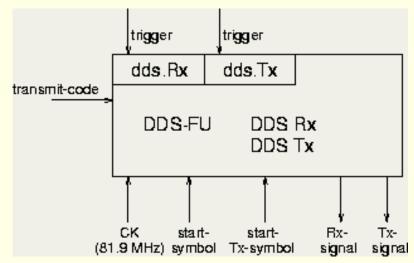

- <u>dds-fu</u>

- Squaring-fu

- Data-in *fu*

- Processor configuration

- o Firmware design

- o Co-Simulation

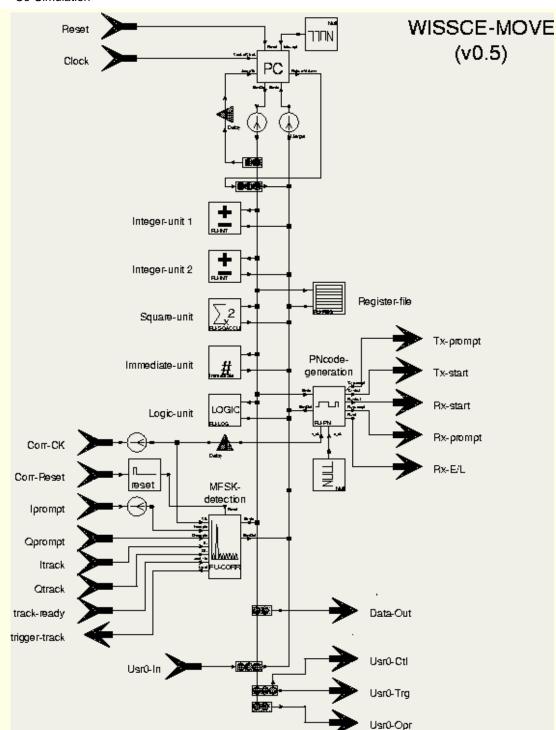

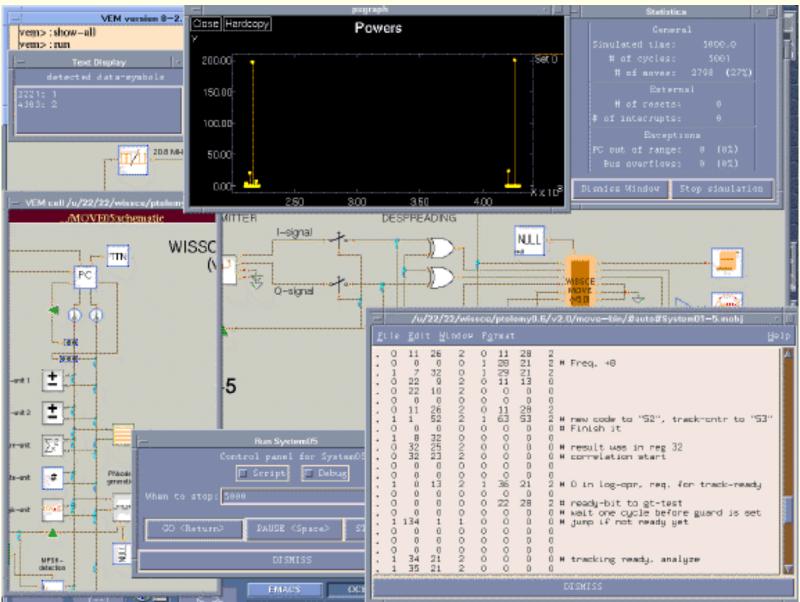

- A co-simulation tool for the -processor

- Simulation level

- Co-simulation

- **■** Conclusions

- o Conclusions

- Conclusions

- Pseudo-Random Noise Sequences

- Selected Code-set

- o Implementing the relative delays

- $\blacksquare$  M(6,5,2,1)-sequence

- $\blacksquare$  M(3,2)-sequence

- References

- Index

- Samenvatting

- About the author

#### © Jack P.F. Glas

This page has been visited times and was last modified on Tue November 12, 1996. Comments and questions can be addressed to the WWW Coordinator.

Next

Up.

Previous Contents Index

Next: Summary Up: Non-Cellular Wireless Communication Systems Previous: Contents

### **List of Figures**

- Wireless, point-to-point communication concept

- Direct-Sequence spreading

- ds-concept, before and after despreading

- Near-Far effect illustrated

- Illustration of the frequency hopping concept

- Embedded system design process

- Structure of a transport triggered architecture

- 3-D view on a Sea-of-Gates circuit

- Receive and transmit frequency bands

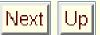

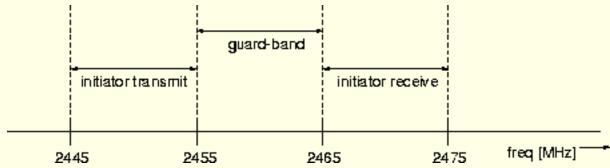

- Trade-off between processing gain and symbol-rate

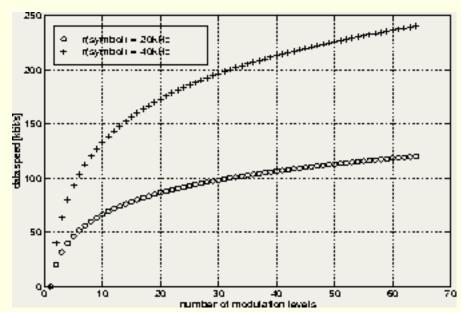

- Trade-off between data speed and number of modulation levels

- A possible user-address

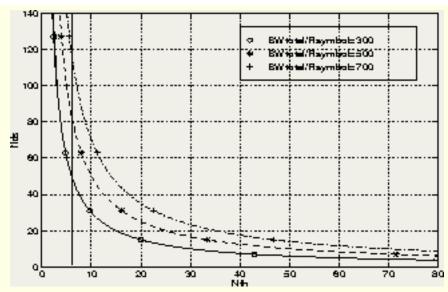

- Trade-off between  $N_{\rm FH}$  and  $N_{\rm DS}$

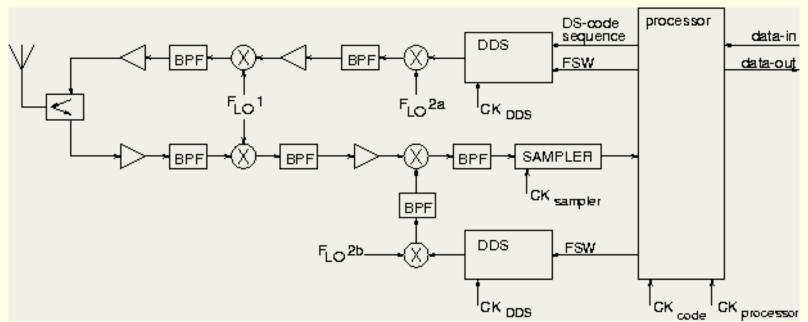

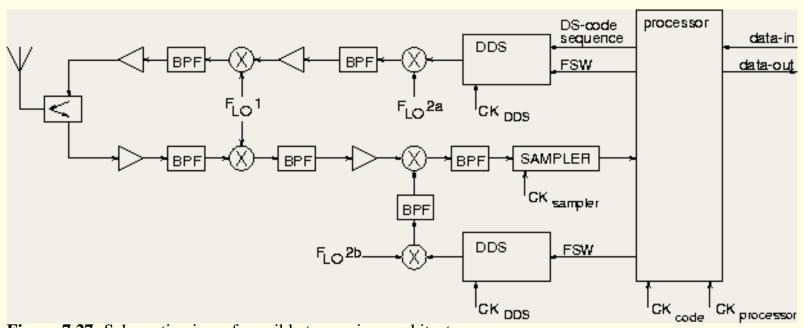

- Low-frequency part of the front-end architecture

- Schematic view of possible transceiver architecture

- Principle of a direct digital synthesizer (dds)

- Proposed clocking scheme

- Effects of input-filtering illustrated

- Partial interference in *ds/fh* spreading scheme

- ma-interference illustrated

- ber verses input-snr

- ber in a fading-environment

- Frequency-domain comparison of a Walsh and an *m*-sequence

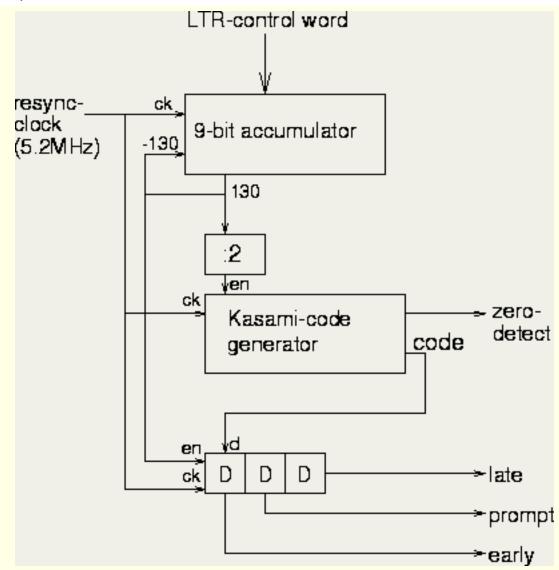

- Kasami-code generator scheme

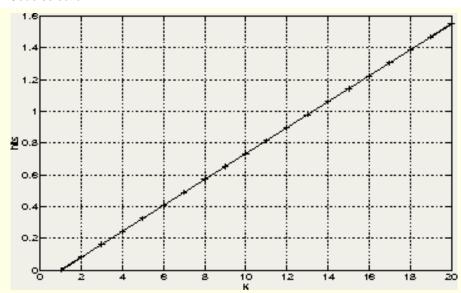

- $E\left\{p_{\text{hit}}(k,K)\right\}$  as a function of K active users

- Implementation trade-offs

- Evaluation of  $tw_{cos}[1, k]$  Evaluation of  $tw_{sin}[1, k]^2 + tw_{cos}[1, k]^2$ .

- Phase dependence for *mfsk*-symbols ``1" and ``8"

- Signal suppression-factors: calculated and simulated

- Limiter *snr*-gain as a function of the input-*snr*

- Sensitivity as a function of the input *snr*

- Phase dependence as function of the input *snr*

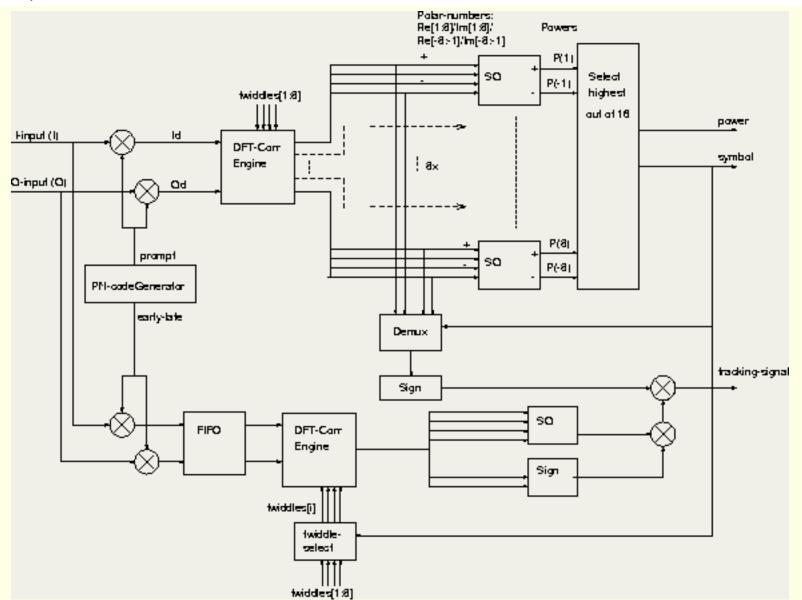

- Data-detection scheme

- ber as a function of the input-snr

- Output power of data-detector as a function of the frequency-error

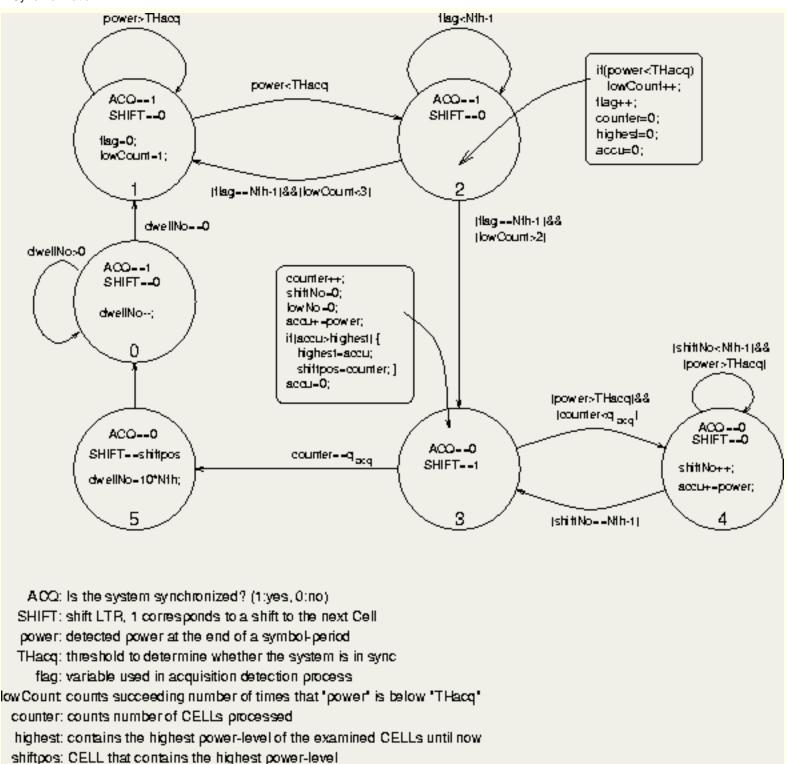

- Code-acquisition algorithm

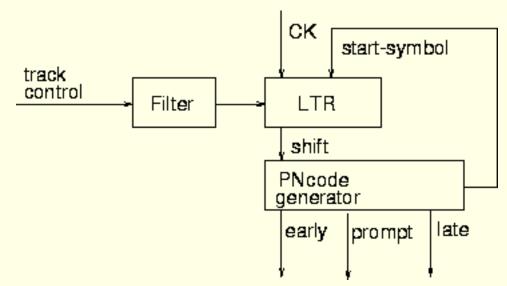

- ltr-control circuit

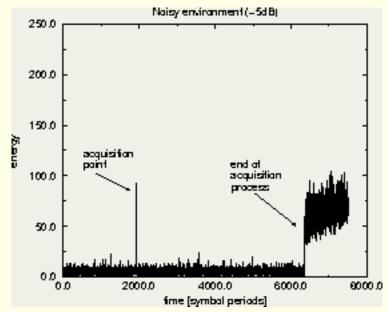

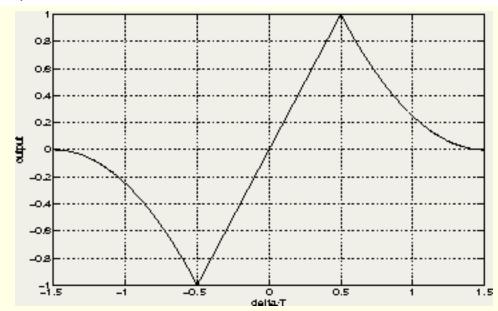

- Acquisition trajectories for different noise situations

- Acquisition trajectory, 2 strong interferers present

- Acquisition trajectory with only one strong interferer

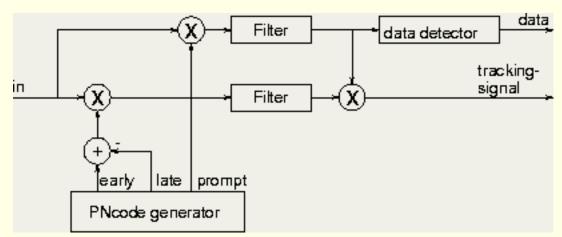

- Typical code-tracking scheme

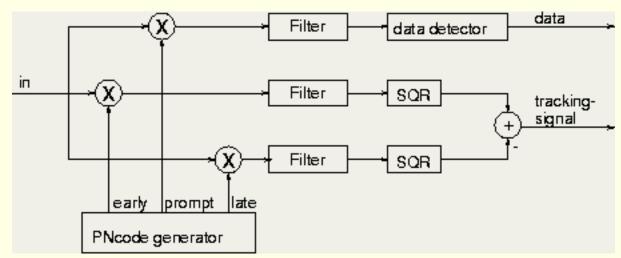

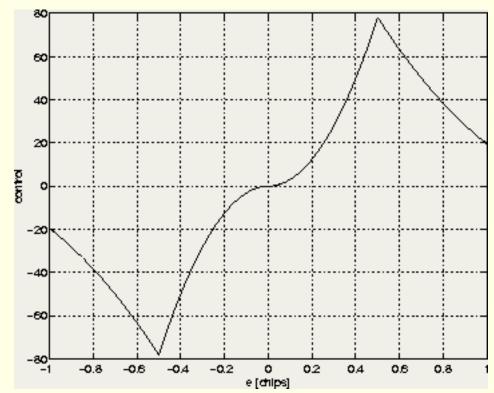

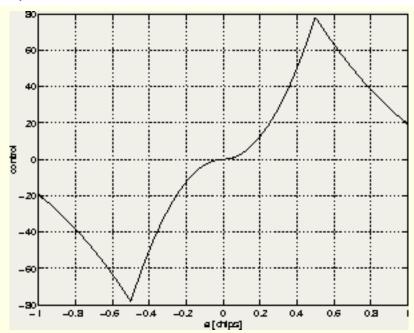

- Typical code-tracking curve

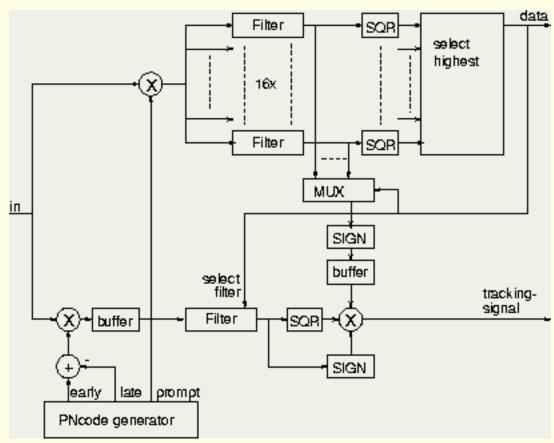

- *mctl*-architecture

- Adjusted *mctl*-scheme

- Tracking curve of the -tracking algorithm

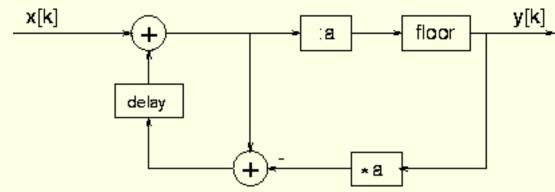

- Code-tracking filter

- Controlling the local time reference (*ltr*)

- Tracking-loop

- Calculated and simulated tracking curves

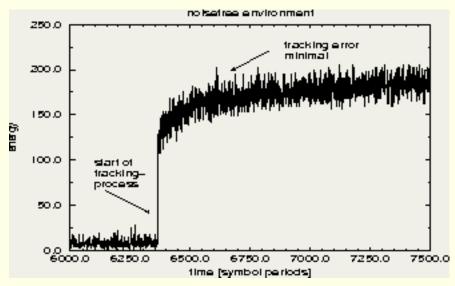

- Simulation of tracking-process

- Schematic view of possible transceiver architecture

- sir-representation of 's receiving process

- Parallelism in the -receiver

- hw/sw-partitioning result

- Structure of a transport triggered architecture with four busses

- Interfacing with the dft-ce-fu

- Interfacing with the *pn-code generator*-FU

- Interfacing with the *dds-fu*

- Interfacing with the Squaring-fu

- Interfacing with the data-in fu

- processor configuration

- Firmware operation during normal operation

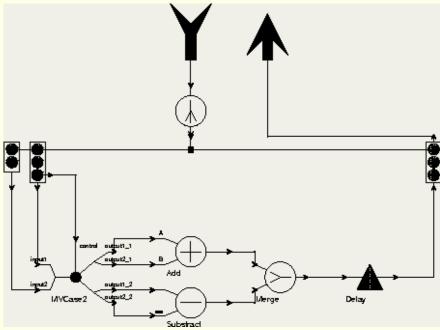

- representation of the integer-unit as a *galaxy*

- Co-simulation in process

%

### © Jack P.F. Glas

This page has been visited times and was last modified on Tue November 12, 1996. Comments and questions can be addressed to the WWW Coordinator.

Next: Multi-Access Up: Non-Cellular Wireless Communication Systems Previous: Preface

### Introduction

People always wanted to communicate and their demands grew with the possibilities offered by technology. Nowadays, modern technology enables mobile communications in many situations. An important component in mobile communications are non-cellular wireless communication systems for short distances.

Wireless communication systems can be roughly divided into two categories: cellular and non-cellular systems. In cellular systems the area to be covered is divided in a number of cells. All communication in a cell goes via a single base-station located in that cell. Hand-over protocols and connections between base-stations enable roaming over cell borders. The consequence of this concept is that both an infrastructure and a complex protocol are required. Non-cellular systems form another category of wireless communication systems for which no infrastructure is required. In this sense the complete system itself is mobile.

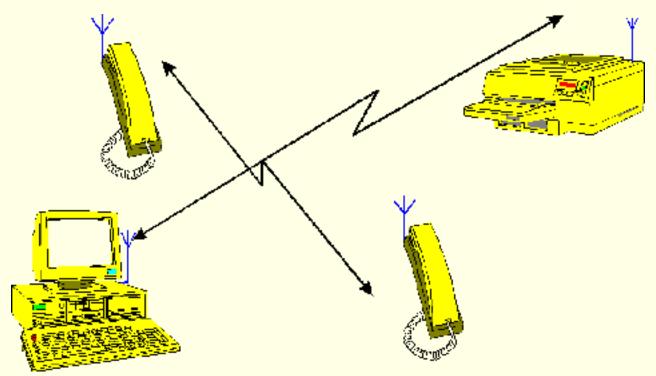

Figure 3.1: Wireless, point-to-point communication concept

This thesis deals with systems providing short distance, multi-access, ad-hoc based, point to point communication links. Shortly, we focus on ``non-cellular wireless communication systems". Applications can primarily be found as indoor data communication systems as illustrated in figure 3.1. As this figure only shows a number of properties of the target communication system, the main

properties are listed below:

- Non-cellular systems do not require an infrastructure. Our target system is a non-cellular communication system for short distances.

- **Multi-access** enables several simultaneous communication links. In the figure two such links are shown.

- Random-access, this term is in this context defined as the ability of users to initiate a communication link at any arbitrary moment.

- **Digital data-communication links** Although not completely clear from the picture, the target system is a digital communication system. Applications can be both data-links and (via a speech-coder) speech-links.

This thesis addresses the different aspects of the realization trajectory of such communication systems. Explaining a design methodology by using a concrete design example has the advantage of exactly showing where ``difficult" points can be found. For this reason, the design trajectory of a communication system referred to as *wissce* is used to illustrate the proposed design methodology.

Concerning such a communication system, a number of sales-points exist. For instance the net data-speed should be high enough to enable reasonable data-transmission speeds. A user would like to have this speed as high as possible, there are however technical limitations. In our system we will therefore use as a constraint a minimum speed of 64 kbit/s which is equal to a single ISDN channel. Another issue is reliability: In most situations a user should be able to initiate a communication link. During communication, the bit error rate (*ber*) has to be acceptable. Other points would be that a user can initiate a transmission link at any arbitrary moment. Also a user does not like long synchronization times or the requirement to install an expensive infrastructure. The possibility to take the system itself and use it at another place would be beneficial. For transmission speed reasons it is is also important to provide duplex connections. In this way transmission and reception at the same time becomes possible. The user's wishes are addressed in more detail in chapter 5 where they will be used as a basis to find a system specification.

- Multi-Access

- CDMA techniques

- Claims of the thesis

- Overview

Next Up Previous Contents Index

Next: Multi-Access Up: Non-Cellular Wireless Communication Systems Previous: Preface

© Jack P.F. Glas

This page has been visited times and was last modified on Wed November 13, 1996. Comments and questions can be addressed to the <a href="https://www.coordinator"><u>WWW Coordinator</u></a>.

Next: CDMA techniques Up: Introduction Previous: Introduction

### **Multi-Access**

An important issue in wireless communication systems is multiple random access: communication links can be activated at any moment while several links can be active simultaneously. As multi-access and random-access are properties mainly determined by the chosen data-communication technique it is important to keep these requirements in mind from the very beginning. Three possible concepts to realize a multi-access communication system are in use:

#### 1. *FDMA*

Frequency Division Multiple Access, commonly used in conventional telephone systems: every user gets a certain frequency band assigned and can use this part of the spectrum to perform its communication. If only a small number of users is active, not the whole resource (frequency-spectrum) is used. Assignment of the channels can be done centrally or by carrier-sensing in a mobile. The latter possibility enables random-access.

#### 2. TDMA

Time Division Multiple Access, applied nowadays in mobile phone systems: every user is assigned a (set of) time-slots. Transmission of data is only possible during this time-slot, after that the transmitter has to wait until it gets another time-slot. Synchronization of all users is an important issue in this concept. Consequently, there must be a central unit (base-station) that controls the synchronization and the assignment of time-slots. This means that this technique is difficult to apply in random-access systems.

#### 3. CDMA

Code Division Multiple Access (Spread Spectrum). A unique code is assigned to each user. This code is used to ``code" the data message. As codes are selected for low cross-correlation properties, all users can transmit simultaneously in the same frequency channel while a receiver is still capable of recovering the desired signal. Synchronization between links is not strictly required and so random-access is possible. A practical application at the moment is the cellular-*cdma* phone system IS-95 [Qua92].

Combinations are also possible, the popular European cellular phone systems *dect* and *gsm* for instance use a combination of *tdma* and *fdma*. There a single transmission-cell is defined by a combination of a frequency channel and a time-slot.

From the above list it is clear that both *fdma* and <u>cdma</u> are candidate transmission techniques to enable multiple random access. There are however a number of reasons for choosing <u>cdma</u> over *fdma*. The first alternative provides [Sch94, SOSL85a, Dix84]:

• **Interference limited operation.** In all situations the whole frequency-spectrum is used. As a result the more active users are present, the higher the interference level will be.

- **Privacy due to unknown codes.** The applied codes are in principle unknown to a hostile user. This means that it is hardly possible to detect the message of another user.

- Applying spread spectrum implies the reduction of multi-path effects. By using a wide frequency-band, the influence of narrow-band fades is reduced.

- Random access possibilities. Users can start their transmission at any arbitrary time (no infrastructure required).

- Good anti-jamming performance. Small-band interference is reduced as explained in the next section.

These were the reasons for selecting <u>cdma</u> as multi-access technique in the non-cellular target communication system. As this choice has a large impact on further design stages, the next section provides an introduction to <u>cdma</u>-techniques.

Next: CDMA techniques Up: Introduction Previous: Introduction

© Jack P.F. Glas

This page has been visited times and was last modified on Wed November 13, 1996. Comments and questions can be addressed to the WWW Coordinator.

Next: Claims of the thesis Up: Introduction Previous: Multi-Access

### **CDMA** techniques

Code Division Multiple Access (*cdma*) is used in spread spectrum systems to enable multiple-access. It is a transmission technique in which the frequency spectrum of a data-signal is spread using a code uncorrelated with that signal and unique to every addressee. As the applied codes are selected for their low cross-correlation values, it is possible to make a distinction between the different signals. An initiator knows the code of the intended addressee and is so capable of activating the desired communication link.

The first applications were in the military field because of the difficulty to jam or detect spread spectrum signals. Nowadays however spread spectrum systems are gaining popularity also in commercial applications (for instance: IS-95 [Qua92]).

If a signal is combined with a code the bandwidth of the original signal increases. The spectrum is "spread" which justifies the name "spread spectrum". At the same time the spectral power density decreases as the total transmitted power stays equal. The ratio of transmission and information bandwidth is therefore an important parameter in spread spectrum systems. This ratio is referred to as "processing gain":

$$G_p = \frac{BW_t}{BW_t} \tag{3.1}$$

which is the ``spreading factor". The processing gain also determines the number of users that can be allowed in a system, the amount of multi-path effect reduction, the difficulty to jam or detect a signal etc. For spread spectrum systems it is advantageous to have a processing gain as high as possible.

Different spread spectrum techniques exist: Direct-Sequence (*ds*), Frequency-Hopping (*fh*), Time-Hopping (*th*) and Multi-Carrier CDMA (*mc-cdma*). It is also possible to make use of combinations. Overviews of the various spread spectrum techniques can be found in [SOSL85a, Hol82, Dix84, PSM82, SH85, YLF94].

We will now concentrate on the two more popular techniques: direct-sequence and frequency-hopping.

### **Direct Sequence**

Direct Sequence is the most popular Spread Spectrum Technique. The data signal is multiplied with a pseudo random bit sequence, often referred to as pseudo random noise code (*pn-code*).

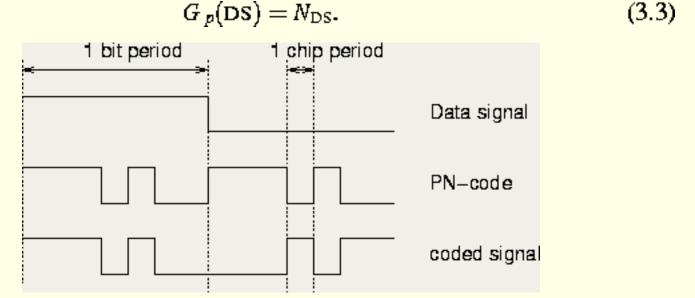

A *pn-code* is a sequence existing of chips (see figure 3.2) valued -1 and 1 (polar) or 0 and 1 (non-polar). Such bit-sequences have noise-like properties like spectral flatness and low cross and auto correlation values, and thus complicate jamming or detection by non-target receivers [Gol67, HdV71, Roe77, Gla92].

Several families of binary pn-codes exist: m-sequences, Gold-codes and Kasami-codes where the latter two can be created by combining a number of selected m-sequences. An usual way to create a pn-code by means of shift-registers with feed-back taps. By putting the feed-back taps at specific positions, the output sequence of a shift register is of "maximum length". The above mentioned code-families [Gol67] have this property. When the length of a shift-register is n, the length of the resulting sequences is [Gol67]:

$$N_{\rm DS} = 2^n - 1. (3.2)$$

In direct-sequence systems the length of the code is equal to the spreading-factor, so:

Figure 3.2: Direct-Sequence spreading

This can also be seen from figure 3.2, where the spreading processes is illustrated, in this example  $N_{\rm DS}=7$ . The bandwidth of the data signal is now multiplied with a factor  $N_{\rm DS}$ . The power contents however stays the same, with the result that the spectral power density is lowered.

The generation of *pn-codes* is relatively easy. A number of shift-registers with feed-back taps is all that is required. For this reason it is easy to obtain a large processing-gain in Direct-Sequence systems.

Figure 3.3: ds-concept, before and after despreading

In the receiver, the received signal is multiplied again with the same (synchronized) *pn-code*. Since a code exists of +1s and -1s, this operation completely removes the code from the signal and the original data-signal is left. Another observation is that the despread operation is the same as the spread operation. The consequence is that a possible jamming or interference signal in the radio channel will be spread before data-detection is performed. In this way jamming effects are reduced (see figure 3.3 [Hen84]).

A large problem with multi-access direct sequence spreading is the so-called near-far effect which is illustrated in figure 3.4. This effect is present when a *cdma* interfering transmitter is much closer to the receiver than the intended transmitter. Although the cross-correlation of ``code A" and ``code B" is low, the correlation of the received signal from the interfering transmitter with ``code A" in the receiver can exceed the correlation of the received signal from the intended transmitter and the correct code. As a result proper data detection is hardly possible.

Figure 3.4: Near-Far effect illustrated

### **Frequency Hopping**

When applying frequency hopping, the carrier frequency is `hopping' according to a unique sequence (an *fh-sequence* of length  $N_{\rm FH}$ ). In this way the bandwidth is increased by a factor  $N_{\rm FH}$  (if the channels are non-overlapping):

$$G_p(FH) = N_{FH}. \tag{3.4}$$

The process of frequency hopping is illustrated in figure 3.5. A disadvantage of frequency-hopping compared to direct-sequence is that it is hard to obtain a high processing gain. A frequency synthesizer is required that is capable of rapidly hopping over a set of carrier (fh) frequencies. The more fh-frequencies, the higher the processing gain and the more demanding the frequency synthesizer becomes.

Figure 3.5: Illustration of the frequency hopping concept

On the contrary, frequency-hopping is less vulnerable to the near-far effect than direct-sequence. Frequency-hopping sequences have only a limited number of "hits" with each other. This means that if a near-interferer is present, not the whole signal is blocked but only a limited number of "frequency-hops". From the "hops" that are not blocked it should be possible to recover the original data-message, for instance by applying error correcting techniques.

Two types of frequency-hopping techniques can be distinguished. In ``fast frequency hopping" the period of a ``frequency-hop" is smaller than a data symbol-period while in ``slow frequency hopping" the period of a ``frequency-hop" is larger than a data symbol-period. Choosing one of those techniques has consequences on the error correcting coding to be applied.

%

Next: Claims of the thesis Up: Introduction Previous: Multi-Access

© Jack P.F. Glas

This page has been visited times and was last modified on Wed November 13, 1996. Comments and questions can be addressed to the WWW Coordinator.

Next: Overview Up: Introduction Previous: CDMA techniques

### Claims of the thesis

This thesis is about the design of a complete communication system. from front-end related issues to digital baseband processing aspects as well as the complete design trajectory: from idea down to a ready for layout description of the target system.

The goal of this section is to mention the highlights that surfaced while working towards this thesis. These points can be grouped into three categories:

#### Concept development of communication systems

concerns the step from idea (application) to system definition. Aside from the combination of all system-concept issues into a system definition, the following points may be of special interest to the reader:

- 1. *Selecting an adequate multi-access technique*As <u>cdma</u>-techniques combine random access with an interference limited system-utilization, they are very suitable to provide multi-access abilities in ad-hoc communication systems. However, all <u>cdma</u>-techniques have their specific disadvantages. The choice of an adequate multi-access technique is therefore an interesting one that also has a large impact on further design stages.

- 2. An acquisition search algorithm independent of a threshold Usual code-acquisition search algorithms make use of a threshold. This threshold however, is difficult to obtain as a number of parameters are unknown to the system. We will therefore propose an acquisition search algorithm that does not primarily depend on a threshold value.

- 3. *Suitable MA-interference analysis*The modelling of the interference from all other users as Gaussian noise is not realistic in non-cellular systems. A more suitable *ma*-interference analysis has been worked out.

- 4. Effectively reducing the effects of near-user interference

Combining salient features of code-acquisition and frequency-hopping leads to an acquisition algorithm independent of near-user interference.

cdma

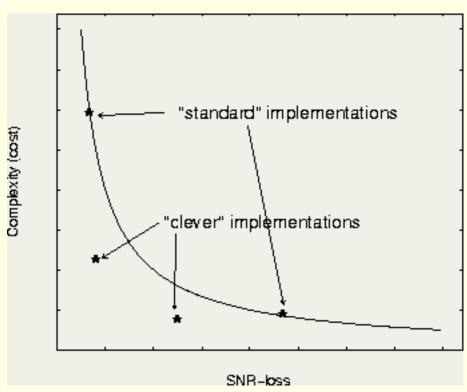

#### Implementation issues in a -receiver

During system implementation, we often find that the requirements of the systems engineer cannot be mapped on the available hardware and software resources. To tackle this problem one can always resort to more advanced (and more costly) resources or degrade the desired properties. In other words: the trade-off between performance-loss and cost becomes visible.

- 1. Complexity reduction of the data-detection algorithm

The complexity of the *mfsk*data-detector (for *mfsk*data modulation see chapter 5) can be reduced by applying a discrete fourier transform while reducing the number of bits used to represent internal numbers.

- 2. Applying 2-level input signals

A considerable reduction of hardware cost can be obtained by limiting the input-signal. This turns out to have only a small effect on the *ber*-performance.

- 3. *Novel code-tracking loop*Through modification of an existing code tracking loop the complexity of the tracking-algorithm is reduced while keeping a satisfactory code-tracking performance.

#### Building a transceiver as an embedded system

includes a novel design-flow to implement an actual design of this kind. A description in the programming language C of the transceiver's algorithm, and trade-off tables for different implementation alternatives function as inputs to the hardware/software partitioning stage. Special attention is asked for:

- 1. Applying automatic tools

When applying an automatic tool, a designer can explore the design space in an efficient way.

Profiling results guide the designer to a ``close to optimal" hardware/software partitioning.

- 2. *The designer stays in control*In spite of the fully automated partitioner, the designer stays in control of the design process.

- 3. *Graphical representation of the algorithm*To exercise this control, a graphical representation of the operation of a system can be of great help in increasing efficiency.

- 4. *Handling real-time constraints*Real-time system design requires a quite different approach from the design of systems without hard timing constraints.

The claims above are verified against the experience with the design of the wissce cdma-transceiver.

Next: Overview Up: Introduction Previous: CDMA techniques

© Jack P.F. Glas

This page has been visited times and was last modified on Wed November 13, 1996. Comments and questions can be addressed to the <a href="https://www.coordinator"><u>WWW Coordinator</u></a>.

Previous

Contents Index

Next: An Embedded Spread Spectrum Up: Introduction Previous: Claims of the thesis

### **Overview**

This thesis discusses a number of important issues existing in the process of realizing non-cellular wireless communication systems. Though we tried to touch all aspects that exist in the design of a communication system, emphasis was on the aspects mentioned in the previous section.

A non-cellular communication system has the advantage to be ``mobile" itself. Users can communicate with each other anywhere as long as their relative distance is within specification. The systems that will be addressed here are also meant for short-distances, for instance to provide ad-hoc indoor communication links. We saw that code division multiple access (cdma) closely fits the ad-hoc nature of non-cellular communication systems for indoor use.

Before making a system design it is important to have a notion of the resources that are available to build the system. Chapter 4 therefore deals with the available resources to implement the baseband processing (synchronization and recovering of the transmitted data-message) of the transceiver. In this chapter we will conclude that an embedded realization almost completely matches our desires towards an implementation. We will also motivate why a transport triggered architecture provides a good processor framework.

The starting point of the system specification will be an analysis of the customer's wishes. Although this aspect was already partly covered in the first sections of this chapter, chapter 5 clarifies the user demands. That chapter also deals with the next step in system design: "How to translate the user-demands into a system-specification?".

Chapter 6 addresses the relation between the bit error rate and the signal to noise ratio before analog to digital conversion. Also specific *cdma* related issues as code-selection and code-synchronization are also addressed.

Before we can actually map the system-specification on the available resources, a major problem has to be solved. The system engineer's ideas usually turn out to be too demanding to fit on the available hardware and software. To this end chapter 7 introduces a number of simplifications to the receiver algorithm, to validate these steps an evaluation of the introduced performance loss will be made.

Now that there is a ``realizable" system design in the form of an algorithm, a start can be made mapping this algorithm on the available resources. A hardware/software partitioning stage is required as we selected an embedded system concept to realize the baseband processing. The hw/sw-partitioningprocess using the partitioning tool *HSpart*is addressed in chapter 8. The chapter concludes with an evaluation of the partitioning results of a practical application.

How the actual co-design is done will be discussed in chapter 9. Here the application specific hardware

modules as well as the transceiver's firmware are described. This chapter also deals with the usage of a co-simulation tool. Co-simulation is important in the evaluation of the cooperation of both hardware and software.

After discussion the important aspects existing in the realization of a communication system, an overall conclusion towards the followed trajectory will be given in chapter  $\underline{10}$ .

For the reader's convenience, a glossary is included at the end that summarizes all symbols and abbreviations used throughout this thesis. An index provides the ease to look up certain terms.

%

Next: An Embedded Spread Spectrum Up: Introduction Previous: Claims of the thesis

© Jack P.F. Glas

This page has been visited times and was last modified on Wed November 13, 1996. Comments and questions can be addressed to the WWW Coordinator.

Previous

Contents

Index

Next: Introduction Up: Non-Cellular Wireless Communication Systems Previous: Overview

## An Embedded Spread Spectrum Processor

- Introduction

- Why an Embedded Realization?

- The design process

- Selecting a Processor-Framework

- Requirements for the Hardware/Software partitioning stage

- Available resources

- Conclusions

#### © Jack P.F. Glas

This page has been visited times and was last modified on Tue November 12, 1996. Comments and questions can be addressed to the WWW Coordinator.

Next: Why an Embedded Realization? Up: An Embedded Spread Spectrum Previous: An Embedded Spread Spectrum

### Introduction

Apart from system constraints, implementation issues are to be considered as well. In this chapter we will discuss the the implementation concept, the *cad*-tools to apply and the available resources. It is important to face these aspects before doing the actual system design. In this way impractical designs can be discarded at an early stage.

Next section addresses implementation problems specific to real-time applications like wireless communication systems. It will be shown that there exist good reasons for applying an embedded system design methodology. The embedded design trajectory will be discussed as well.

In designing an embedded system the choice of processor is of great importance. The performance and structure of such a processor influences the choice of what functionality to implement in software under the existing constraints. The choice of a processor architecture is discussed in section 4.4.

Once a target processor architecture is chosen and the system is formally described, the hardware/software (hw/sw) partitioning stage can start with the automatic generation of profiles. Section 4.5 outlines the requirements we have for the results of this stage.

#### © Jack P.F. Glas

This page has been visited times and was last modified on Tue November 12, 1996. Comments and questions can be addressed to the WWW Coordinator.

Contents Index

Next: The design process Up: An Embedded Spread Spectrum Previous: Introduction

### Why an Embedded Realization?

Most transceiver architectures have a natural partitioning into two parts: an analog front-end and a digital back-end. The implementation of the latter, and the baseband processing (synchronization and recovering of the transmitted data-message) in particular will be the focus of the following discussion. To enable this discussion, an unambiguous algorithmic description of the digital back-end is required. An additional requirement is that verification of the system should be possible. For this reason it is important that the algorithmic description can be simulated easily. A programming language like C can for instance be used for this purpose.

Baseband operations exist to a large extent of controlling functions and mathematical processing. For this reason it would be appropriate to implement the baseband processing completely in software. Software implementations have the advantages of being cheap (no application specific hardware) and flexible. However, software is in general slow compared to hardware.

Whether the complete operation can be implemented in software depends on the timing constraints that exist for a certain application. For the target system it is already questionable whether today's computers are sufficient. Consequently, it is infeasible to implement the complete baseband processing on the resources we have available.

Real-time systems with hard timing constraints like TV-sets, automotion systems, radio-receivers etc. do not function properly if timing constraints are not met. This in contrast to systems which do not show hard timing constraints like laser-printers, washing-machines etc. In such applications timing affects the speed, not the functionality.

Obviously, if a TV-set is on average not able to process one frame before the next frame starts, functionality is lost. Most communication systems are examples of real-time systems with hard timing constraints. Like in the TV-set example, processing has to be completed within a fixed frame, otherwise the system does not work correctly.

As a consequence, there is not a simple trade-off between cost and speed. To enable proper operation, a minimal processing speed has to be satisfied if the performance is fixed. Due to the hard timing constraints it is unlikely that implementing the transceiver exclusively in software will still be possible. A logical solution now is to move certain functionality from software into hardware to preserve software domination.

This observation leads to an embedded system: an embedded system implements certain real-time functionality by using an optimal combination of dedicated hardware and software working together and concurrently. Another property of an embedded system is that it runs the same software over and over again.

Once a communication procedure is completely specified, it has to be decided what functionality to put in hardware. Traditionally an embedded system was just a piece of hardware and one or more processing elements which cooperated to perform a certain functionality. After the manual partitioning of what functionality to implement in hardware and what to do in software the two parts were implemented independently.

Nowadays requirements concerning efficiency are getting more stringent. For this reason the interaction between hardware and software has to be taken into account in the design process. By designing the hardware and software parts of a system ``together", the barrier between the two parts lowers. It now becomes possible to move functionality from hardware to software and the other way around.

Usually an embedded design trajectory starts by writing an algorithmic description of the target system in a high-level language. Then the designer is in control of choosing a processor, doing the *hw/sw*-partitioning and designing the different parts [Str94].

Different opinions exist on the process of hardware/software partitioning. In many situations, people define an embedded system as consisting of a combination of a general purpose processor and a co-processor [EHB93], or as a standard programmable element together with an *asic* [GCD94]. In these situations, a gap between hardware and software still remains. To reduce the distance between hardware and software further, the software and hardware parts of a system can be implemented in the same processor framework. Such an framework can for instance consist of a single chip.

As the hardware and software parts are designed concurrently, the hardware and software parts are now optimally ``tuned" to each other. In that case the processor-architecture can be configured in such a way that user-defined functionality can be included as well as general purpose functionality. The question of <a href="https://www.partitioningnow.org/">hw/sw-partitioningnow.org/</a> becomes the question of what application specific functionality to include in the processor framework.

Still the question remains of what functionality to implement in hardware and what functionality to put in software. In our point of view the designer should be presented a lot of profiling results which can be used by the designer to efficiently evaluate the large design space.

A number of issues exists in the partitioning process:

- 1. As a designer is usually a hardware designer *or* a software designer, he/she will have an eye for either an hardware or an software optimization, not for the complete system. A tool that gives "objective" profiles has advantages from this point of view.

- 2. As the size of the systems grows, it is getting more and more difficult for a designer to keep track of all relevant details.

- 3. An automatic system is capable of reviewing a large number of sample-points from the large design space of the *hw/sw*-partitioningprocess. From there the designer is able to get a `feeling' for the possibilities.

- 4. An automatic tool enables the development of tools with which non-experts can arrive at acceptable designs.

- 5. Although we state that it would be advantageous that non-experienced designers will be able to solve the *hw/sw*-partitioningproblem, there is no tool available to us capable of providing this service. It is therefore still required that a designer stays in control of the partitioning process.

To summarize: Implementing the baseband processing of a communication transceiver completely in software would nicely fit its nature and provide a flexible and cheap solution. In many situations however, hard timing constraints disqualify this approach. As a result, part of the functionality has to be implemented in hardware. Therefore an embedded implementation is proposed to obtain an efficient design. In such a system the hardware and software parts form a single framework. An *hw/sw*-partitioningtool is required to help the designer obtaining a *hw/sw*-partitioningthat can be verified using co-simulation in a later stage.

Next: The design process Up: An Embedded Spread Spectrum Previous: Introduction

© Jack P.F. Glas

This page has been visited times and was last modified on Tue November 12, 1996. Comments and questions can be addressed to the WWW Coordinator.

Previous

Contents Index

Next: Selecting a Processor-Framework Up: An Embedded Spread Spectrum Previous: Why an **Embedded Realization?**

# The design process

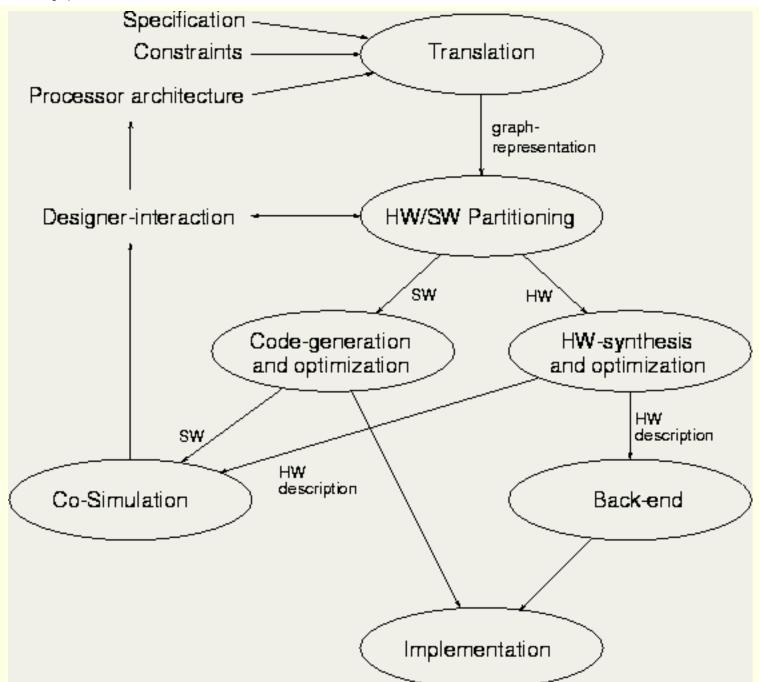

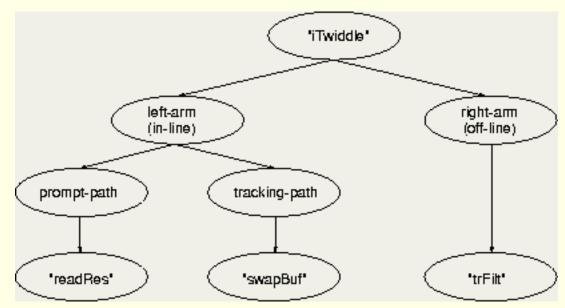

There are three inputs to the design process:

- Specification An algorithmic description that specifies the behavior of the system.

- **Constraints** There are constraints to be satisfied during the implementation stage. These can be for instance timing, area or power constraints. We will concentrate on both timing and area constraints.

- Processor architecture The choice of a processor architecture family is essential as it has a large influence on the costs of software implementations. It is however time costly to evaluate different processors and the choice should off-line: it affects the partitioning process from the very beginning.

After supplying these inputs a translation stage starts. Here the system specification is analyzed to select those functions for which the *hw/sw*-partitioningquestion plays. This translation results in two graphs: firstly a control-flow graph that shows the sequence and parallelism of operations to be performed. And secondly a data-flow graph that represents the data transport between operations.

For all functions and variables appearing in these graphs cost-data has to be supplied. This data appears in the form of tables: for all possible implementation choices and interfaces, cost-numbers on area and timing are provided. As a fast alternative usually takes more area than a slow implementation and vice versa, these tables will typically show a trade-off between area and speed.

The graphs, constraints and delay/area trade-offs are the input to the hw/sw-partitioningstage. During this step the hw/sw-partitioning design space is evaluated to arrive at an optimal partitioning for the given inputs. This is an interactive and iterative process: before a partitioning run, the designer is able to lock functions into certain alternatives and to let the tool optimize for sets of remaining functions. If the result is not satisfactory another partitioning run can be started.

Once a partitioning result is accepted, the implementation alternatives should be implemented. To verify the cooperation between hardware and software however, first a co-simulation of the selected configuration is performed. On basis of the co-simulation results we may want to start the hw/sw-partitioningprocess again or change the input specification. After obtaining satisfactory simulation results, the actual hardware can be realized.

Figure 4.1: Embedded system design process

Next Up Previous Contents Index

**Next:** <u>Selecting a Processor-Framework</u> **Up:** <u>An Embedded Spread Spectrum</u> **Previous:** <u>Why an Embedded Realization?</u>

© Jack P.F. Glas

This page has been visited times and was last modified on Tue November 12, 1996. Comments and questions can be addressed to the WWW Coordinator.

Next: Requirements for the Hardware/Software Up: An Embedded Spread Spectrum Previous: The design

process

# Selecting a Processor-Framework

It is evident that lowering the barrier between software and hardware as much as possible leads to an efficient implementation in the sense that hardware and software almost seamlessly work together. However, before performing the hardware/software partitioning stage, a processor framework has to be selected. The choice of a processor framework is important: it determines to a large extent the costs of the software implementations. The following requirements are formulated for a processor framework:

- 1. *Generality*It should be possible to fully configure the processor core with desired ``general purpose" functionality.

- 2. Easy incorporation of dedicated functionality

Dedicated functionality also has to be implemented within the processor framework.

- 3. *Uniform interfacing*The interface between the processor-core and general purpose functionality or application specific functionality should be uniform. If however, application specific functionality has external I/O, a processor-hardware synchronization protocol is likely to be required.

- 4. *Various execution times*Different functionality will show different execution times, the processor has to adapt to this property.

- 5. *Instruction parallelism*An important advantage of an hardware realization is that it enables parallel processing. If the processor architecture is sequentially going through a set of operations, or stays idle while application specific functionality is active, this advantage is lost.

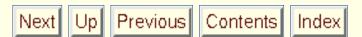

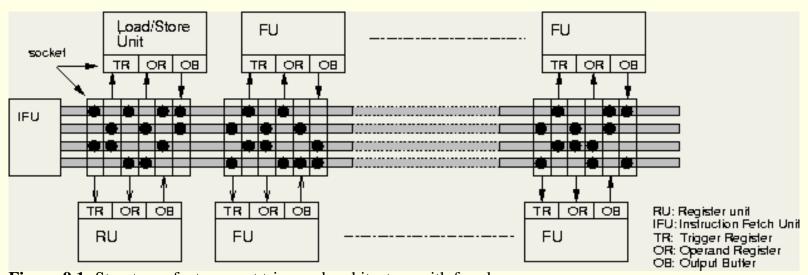

The so-called transport triggered architecture (*tta*) [Cor95] closely fits these requirements. This clocked architecture is illustrated in figure 4.2. Central to a *tta*-architecture is a set of busses. Different kinds of functional units (*fus*) can be connected to these busses via so-called *sockets*.

Figure 4.2: Structure of a transport triggered architecture

An *fu*typically has three registers: an operand register, a trigger register and a output-register. The operand and trigger registers are inputs. As soon as a trigger-register detects new data, the *fu*starts its operation. After a certain ``latency'' (execution time in clock cycles), the result appears at the output-register. For example, to add two numbers *a* and *b*, *a* is moved to the operand register—of the adder-*fu* and *b* is moved to the trigger-register. After that, the addition starts and a number of cycles (latency) later the result can be read from the output-register.

The advantages of this architecture are its simplicity and flexibility while preserving its completeness: it is still possible to use the processor in general purpose situations. The flexibility however is also creating a new problem: how to handle the large design-space? We already mentioned that the number and kind of *fus* can be chosen freely, but other parameters have to be specified as well.

#### bus width

The bus width determines the size of the words to be processed by the *fus*. Typically multiples of 8 are chosen, today's computers often show a bus width of 32 [Cor95]. This number however, is likely to be an overkill for embedded systems as our target system. As there are a number of busses, reduction of the bus width leads to a smaller area-occupation. As a result a trade-off between the possibility to handle large numbers and area-occupancy becomes visible.

#### number of busses

As the *fus* can operate concurrently, the degree of potential parallelism is determined by both, the number of *fus* and the number of busses. As a bus consists of a number of data lines (bus width), reducing the number of busses again leads to substantial area saving (potential parallelism against area).

#### width of address-bus

Beside a data-memory, also an instruction-memory exists. This instruction-memory contains the moves that have to be performed. The wider the address-bus, the more *fus* can be addressed in a processor and the more flexible the processor becomes (flexibility against area).

#### number of register-units

As a register-file enables the processor to have fast access to temporarily data, the size of the register file determines to a certain extent the speed of a process (speed against area). A constraint towards the minimum size of the register-file however exists (to enable scheduling [Hoo96]).

Concluding: we saw that a transport triggered architecture is quite suitable as an processor framework in an embedded system such as our target system. This architecture will be the basis for implementing the baseband processing. In chapter 9 a detailed description of the mapping the receiver algorithm onto this processor is given.

Next: Requirements for the Hardware/Software Up: An Embedded Spread Spectrum Previous: The design process

© Jack P.F. Glas

This page has been visited times and was last modified on Tue November 12, 1996. Comments and questions can be addressed to the WWW Coordinator.

Up Pr

Previous Contents

Index

Next: Available resources Up: An Embedded Spread Spectrum Previous: Selecting a

Processor-Framework

# Requirements for the Hardware/Software partitioning stage

Evaluating the large design space of hardware/software partitioning is initially impossible without the usage of automatic tools. To this end, tools are being developed. Examples are *cosyma* [EHB93], *vulcan* [GCD94], *paes-i*[BISH96] and *HSpart* [KO95, Kar95].

These tools require cost-data on the possible implementation alternatives to find profiles. As the cycle-time is bounded below by the chosen processor architecture, we will express timing-costs in terms of latencies: the number of cycles that it takes to complete an operation. Area cost is expressed in terms of gate usage.

As cost-data is not available at this stage, the designer will usually have a hard time collecting it. A safe way to do this, is by designing the actual software and hardware implementations and then use profiles and simulations. This however introduces the need for extra manpower. In general even the data resulting from such exercises will contain uncertainties which in their turn introduce the risk of obtaining inefficient or even invalid partitioning results. So investing much effort in the extraction of cost-data is not a guarantee for obtaining an optimal result.

This problem can be coped with by applying *HSpart*, a tool built on top of the <u>castle</u>-environment [TSV94]. The application of this tool avoids the requirement to supply exact cost-data. The algorithm implemented in this partitioner uses imprecise (possibilistic) input data: supplying a "most-possible" value, a "minimum" value and a "maximum" value is sufficient. Usually it is not difficult to find these numbers. For instance area-costs: a minimum value can correspond to the number of gates you need without wiring while the maximum value can correspond to the result a fast layout-run. The influence of the most-possible value can be controlled. The salient feature of *HSpart* is the possibility to control the risk of getting out of the specification due to wrong-guessed cost-values.

To summarize, we expect the hw/sw-partitioning-stage to be guided by an automatic tool but controlled by the designer. It should provide the following:

- 1. Profiling results of possible hardware/software partitionings.

- 2. Suggestions concerning the amount of ``standard functionality" to include in the processor framework.

- 3. Suggestions how to handle clustering: what functionality can be combined to arrive at a reasonable number of application specific functional units?

Requirements for the Hardware/Software partitioning stage

Next: Available resources Up: An Embedded Spread Spectrum Previous: Selecting a

Processor-Framework

© Jack P.F. Glas

This page has been visited times and was last modified on Wed November 13, 1996. Comments and questions can be addressed to the WWW Coordinator.

Next: Conclusions Up: An Embedded Spread Spectrum Previous: Requirements for the Hardware/Software

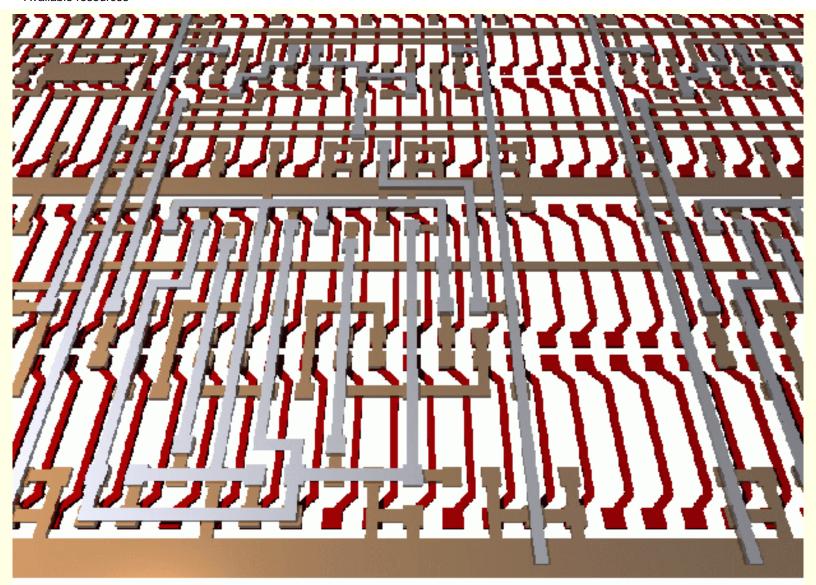

# **Available resources**

The choice of what resources to use is essentially based on the the available resources at the circuits and systems group in Delft. The <u>ocean</u> [GS93, Str94] tool-set provides placement and routing for semi-custom Sea-of-Gates *ic*-design. At the same moment such *ics* can be further processed at <u>dimes</u>.

The digital part of the transceiver should therefore, if possible, be implemented on a single Sea-of-Gates (sog) chip. Such a chip is based on a semi-custom ic fabrication process available in Delft and uses the *fishbone* image: a gate-isolation image in a 1.6  $\mu$  cmos process with 2-level metallization. A single chip has has about  $100.000 \, n/p$ -mos transistor pairs. On this chip the hardware-functionality as well as the software functionality should fit. The sea-of-gates design system <u>ocean</u> is being used for prototyping. As an illustration figure 4.3 gives a 3-D view of part of a Sea-of-Gates circuit. Achievable clock speeds for a processor on Sea-of-Gates are up to 50 MHz.

Figure: 3-D view on a Sea-of-Gates circuit

#### © Jack P.F. Glas

This page has been visited times and was last modified on Wed November 13, 1996. Comments and questions can be addressed to the WWW Coordinator.

Next: Hybrid DS/FH Spread Spectrum Up: An Embedded Spread Spectrum Previous: Available

resources

# **Conclusions**

The goal of this chapter was to find an implementation frame to be used to realize the digital baseband processing of the target communication system. We concluded that a complete software realization fits the nature of the operations to be implemented, however, such an approach is out of the question because of the existing hard timing constraints. On the other hand a complete hardware realization is not flexible and expensive. An approach in which hardware and software cooperate seamlessly provides a solution. This is what we call an embedded system.

The design-flow existing in embedded system design differs from usual design flows in the sense that the operation of the target system is partitioned into hardware and software functionality. We saw that an automatic tool to guide the designer through the large design space is highly desirable to efficiently perform the partitioning.

An important choice is to select an appropriate processor framework. For efficiency reasons we make this choice before the partitioning process starts (to limit the enormous design space). After evaluating our requirements towards such a processor framework, we selected a transport triggered processor architecture (*tta*) to be the core of our embedded system.

Another way to limit the design space to a reasonable size was by selecting the available resources. At the end of this chapter an indication of these resources was given.

%

#### © Jack P.F. Glas

This page has been visited times and was last modified on Tue November 12, 1996. Comments and questions can be addressed to the WWW Coordinator.

Up Previous

Contents

Index

Next: Introduction Up: Non-Cellular Wireless Communication Systems Previous: Conclusions

# Hybrid DS/FH Spread Spectrum Communication System

- Introduction

- System Specification

- Clock control

- Fixing the system parameters for wissce

- Conclusion

#### © Jack P.F. Glas

This page has been visited times and was last modified on Tue November 12, 1996. Comments and questions can be addressed to the WWW Coordinator.

Next: System Specification Up: Hybrid DS/FH Spread Spectrum Previous: Hybrid DS/FH Spread

**Spectrum**

# Introduction

The system specification stage can be characterized as a translation of user demands into a technical specification. In this chapter we will concentrate on the trade-offs that exist during the system design stage. As an illustration, the design of a non cellular communication system referred to as *wissce* will be explained. This acronym ``*wissce*" stands for Wireless Indoor Spread Spectrum Communication Equipment. This system will function as example of the design process throughout the remainder of this thesis.

This chapter is primarily focussed on system-level aspects. We however will keep in mind the implementation issues addressed in the previous chapter. In the next section the trade-offs that exist between the system parameters will be discussed. Section <u>5.3</u> addresses the way the various clocks in <u>wissce</u> can be derived from a single time-base. The actual choice of parameters is made in section <u>5.4</u>. At the end a conclusion shortly summarizes the results of the system specification stage and provides an summary of <u>wissce</u>'s system specification.

#### © Jack P.F. Glas

This page has been visited times and was last modified on Wed November 13, 1996. Comments and questions can be addressed to the WWW Coordinator.

Previous

Contents Index

Next: Clock control Up: Hybrid DS/FH Spread Spectrum Previous: Introduction

# System Specification

In chapter 3 the application domain of the target communication system was already briefly described. The goal of this section is to clarify the communication concept and evaluate the user demands. In this way a basis for the system specification can be found.

The concept of non-cellular communication systems requires no installation effort. A complete system only consists of a set of transceivers and is therefore mobile itself. A group of people might for instance go somewhere and still be able to communicate with each other as long as their relative distance is within specification.

So a non-cellular solution provides an enormous flexibility while it is also keeps prices acceptable in the sense that no additional investment in infrastructure is required, on the condition that the price of a single transceiver is comparable to the price of a mobile in a similar cellular system.

To enable communication, connections have to be made which requires a protocol. Such a protocol should fit the flexible nature of the proposed application domain and therefore has to be simple. A simple and effective protocol which will be used in the following, works as follows: an initiator starts transmission by making a call to an arbitrary other device (addressee). To this end the initiator transmits using the address (*cdma*-code) of the intended addressee. Once the addressee acquired synchronization, it gives an acknowledgement back to the initiator. If the initiator can synchronize to this message within a certain amount of time, the transmission of the intended data-message can start. The consequence of this approach is that during the synchronization stage both transceivers are transmitting simultaneously. During ``normal" data communication this duplex connection is also required to remain synchronized. As a result the transmission system must provide full-duplex communication links.

Now that the non-cellular concept is explained, the user demands can be evaluated to fix technical parameters.

#### 1. Universal usage

Paramount to the user is undisturbed, low risk usage. For a large number of countries this means that a communication system has to obey legal requirements. The dutch situation requires spread spectrum communication systems to operate in the 2.4 GHz ISM-band. In most other western countries this frequency-band is available as well. The usage of this frequency band imposes a number of restrictions. The most stringent restriction is the bandwidth limitation. In the following we will refer to this user-demand as "meeting legal requirements".

#### 2. Reliable operation

Users wish error-free transmission. As complete error free transmission is not possible, the error probability should be minimized. In data communication it would be possible to "retransmit" erroneous messages on the cost of a lower transmission capacity. For voice applications however, this is not possible.

#### 3. *In-door usage*

The system is targeted for short distances so an important application will be as indoor communication equipment. Consequently operation in the (hostile) in-door environment should be possible.

#### 4. High transmission capacity

Pure data communication applications nowadays demand high transmission speeds. The transmission speed is however limited by the available bandwidth and the number of users that have to be allowed in the system.

#### 5. High active user capacity

A difference can be made between ``active user capacity" and ``total user capacity". The first capacity is determined by the amount of interference that can be allowed in the system. The total user capacity however, is determined by the number of available addresses (*cdma*-codes). At this point the focus is on the ``active user capacity".

#### 6. Large area coverage

An important consideration is the maximum allowed distance between users. The system is meant for short-distances. For flexible usage however, this ``short-distance" should be not too short. On the other hand the larger the distance, the higher the energy usage will be and the more interference will be generated for the other (near) users. The latter results in a worse mean receiving quality.

The further users are apart, the worse the receiving quality will be. So the radio link will fail ``softly".

#### 7. Low purchasing costs

The complete communication systems consists of only transceivers and is meant for the mass-market. In comparison with cellular systems, a non-cellular approach provides flexibility. It is however important that the price of a transceiver is comparable to that of mobiles in a similar cellular system. The purchasing costs therefore should be low.

#### 8. Low operation costs

Power consumption should be low to decrease operation costs. A service provider is not involved as the system does not depend on an infrastructure.

#### 9. Flexibility

The system should be flexible in the sense that many different applications can be allowed.

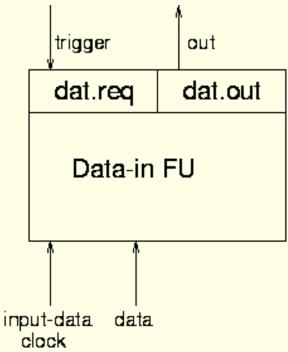

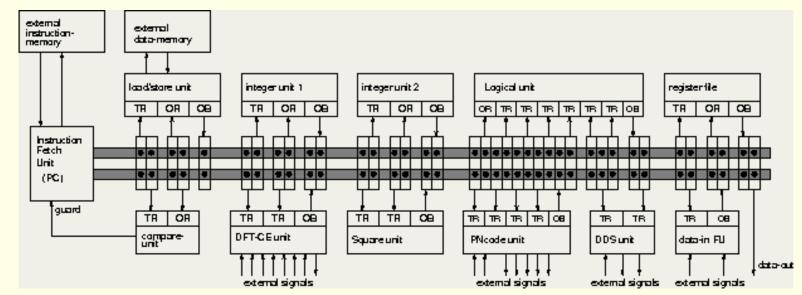

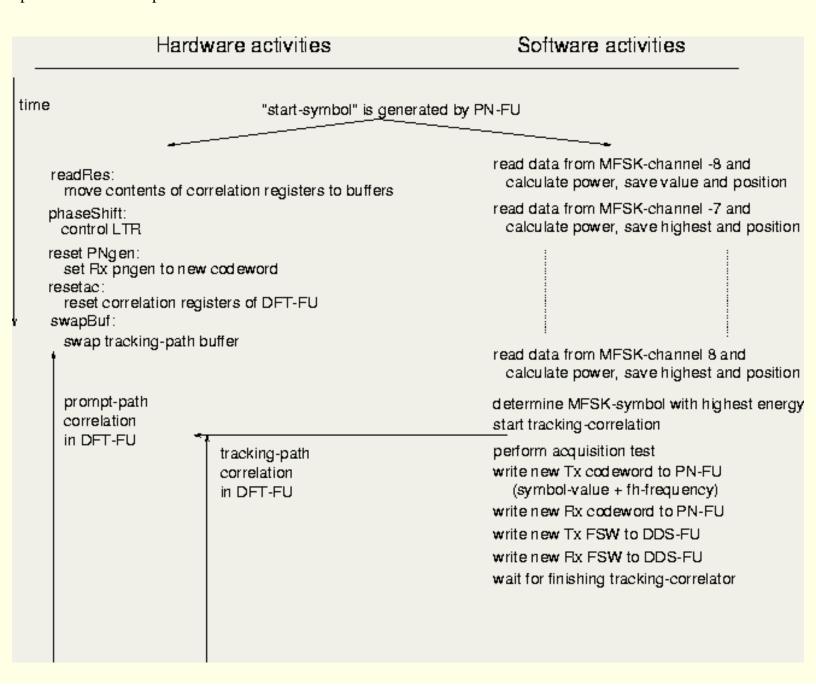

#### 10. Mobility